如何通过混合信号仿真优化硅光子学

Silicon photonics 正在重塑数据中心的未来。但工程师需要更先进的仿真工具来将这些轻型吊索组件与电子设备集成。

本文引用地址:https://www.eepw.com.cn/article/202506/471472.htm当今的计算和通信应用程序需要前所未有的处理能力和高带宽内存访问。以光速传输的数据正在成为解决方案。

在数据中心,GPU 通常在 AI 训练和推理期间每秒相互传输数 TB 的数据,远远超过了传统铜缆互连的限制,后者的最高速度为每秒数百兆比特。光互连已成为满足这些需求的解决方案,它使用光束以高达 100 Gb/s 的速度传输数据。但是,设计和验证此类复杂系统需要高级仿真工具来对其性能进行建模,并确保组件的无缝集成。

光连接的未来完全与硅光子学有关。该技术将光学和电子元件合并到单个硅芯片中,从而实现高效和高带宽的数据移动。它在数据中心互连、5G 无线网络、城域网和长途电信、高性能计算 (HPC) 和 AI 等领域变得越来越普遍。它还有可能在量子计算中发挥作用。

如今,这些系统包含复杂的模拟和数字组件网络。但是,将硅光子学集成到这些混合信号系统中,会给芯片设计人员和系统工程师带来更多的复杂性。对电气、光学和数字域执行精确仿真的能力对于开发 AI 工作负载和其他应用程序所需的高带宽、低延迟连接至关重要。

硅光子学的构建模块

从根本上说,硅光子学就是将光速带入 CMOS 世界。

通过将激光器、波导和光电探测器等组件集成到单个基板上,这些系统可以精确控制光线。激光器和发光二极管 (LED) 等光源将电信号编码为可见光或红外光,将电子转换为光子。相比之下,光电二极管和其他光探测器执行相反的过程,将透射的光转换为电信号。

光波导充当光的管道,类似于铜线传输电信号的方式。虽然激光器在集成到系统之前是单独制造的,但波导往往直接放置在硅芯片上。在许多情况下,这些波导可以进行电气控制,从而能够动态控制其折射率,以调整透射光的相位和强度。因此,这些组件可用于过滤或调制光束。

光耦合器和分路器进一步增强了系统功能。合路器合并来自多个来源的信号,允许基于干扰的调制,而分路器将光信号分成几个不同的输出,功率分配成比例。这些组件构成了硅光子学的构建块,对于数据中心的波分复用 (WDM) 等应用至关重要。

Silicon Photonics:从服务器内部到 SoC 内部

硅光子系统以各种配置部署,从安装在 PCI Express (PCIe) 卡上或直接安装在主板上的独立设备到通过光学背板连接的整个服务器机架。

但最新的创新之一是将光学小芯片集成到多晶粒系统中。这些封装的核心是系统级芯片 (SoC),主要是数字式的,通常包含数百亿个晶体管。它们充当服务器或网络交换机的主处理单元,使用电气 I/O 与系统中的其他芯片(或者,在交换机的情况下,与可插拔光学器件的端口)通信。然而,半导体公司的目标是将硅光子收发器小芯片集成到同一封装中,以克服电气 I/O 的限制。

在基于小芯片的光互连领域,Intel 最近推出了一种新的 OCI 兼容光小芯片,通过单模光纤提供 64 个双向通道和高达 4 Tb/s 的吞吐量。IBM 的共封装光学模块直接与主机芯片集成,将海滨光纤密度提高了六倍。

硅光子学小芯片用作高速光收发器。它们通过光纤而不是铜线在同一服务器、同一机架甚至不同机架中的芯片之间移动数据。这些架构表明,对结合模拟、数字和光域的异构系统的精确仿真的需求日益增长。

共封装光学器件的挑战在于,硅光子学小芯片集成了光学和电子元件,从而创建复杂的混合信号系统,需要严格的仿真和验证才能确保最佳性能。此外,芯片设计人员和系统工程师还必须考虑广泛的其他因素,从散热和功率效率到信号 (SI) 和电源完整性 (PI)。

这些架构需要改变系统级交互的建模和验证方式。随着光学元件越来越接近处理内核,逻辑仿真必须不断发展,以捕获不同时间尺度和抽象级别的电光交互。

例如,光互连与射频前端的集成(就像最新的异构硅光子接收器设计一样)强调了对精确行为和布局感知建模的需求。异构光子 IC 的总结进一步强调了跨光学、模拟和数字域的协同仿真的作用。

这些发展加强了可扩展的混合信号仿真和建模框架的重要性,这些框架可以在功能、物理实现和系统性能之间架起桥梁。

模拟多晶片硅光子系统的挑战

然而,设计具有集成硅光子元件的多晶粒系统面临着独特的挑战。

半导体供应商通常为支持硅光子学的特定工艺节点提供工艺开发套件 (PDK),其中包含电子和光学元件的精确模型。在大多数情况下,这些模型采用严格的模拟格式,例如 SPICE 或 FastSPICE,或采用硬件描述语言 (HDL),例如 Verilog-A、Verilog-AMS 或 VHDL-AMS,所有这些都可用于模拟仿真。这些模型在模拟域中为您提供高精度和相对较快的性能。

然而,使用模拟仿真工具进行混合信号验证(也称为模拟混合信号 (AMS))可能会导致仿真速度非常慢且耗费资源。光子系统的复杂性加剧了这些挑战,需要新的方法来确保精度和效率。

即使在相对简单的 implementations 中,设计和验证过程也可能很复杂。例如,使用不同波长的多个不同光源的发射机小芯片必须确保光纤另一端的接收机小芯片能够准确分离和处理这些信号。系统必须验证光波导和调制器在各种电压条件下是否有效工作。当 chiplet 被设计为充当收发器时,复杂性会显著增加。

实数建模:混合信号仿真的下一阶段

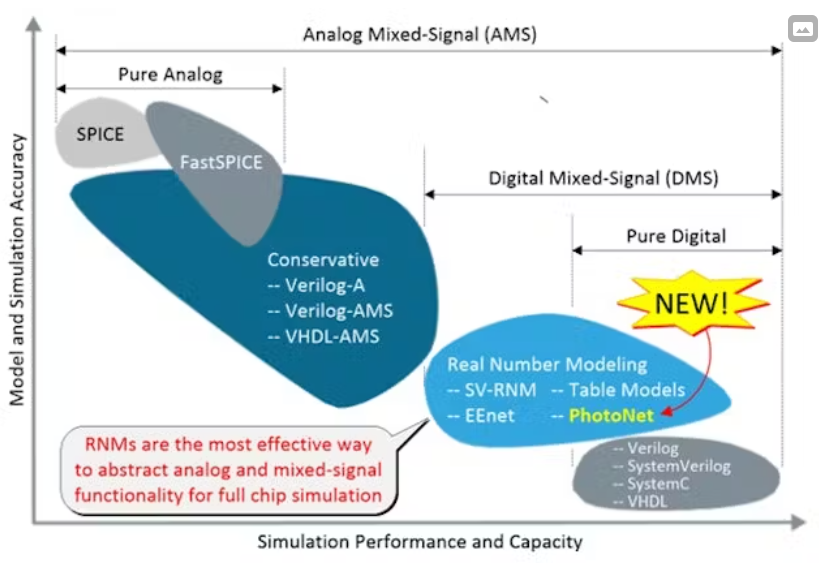

实数建模 (RNM) 是弥合模拟域和数字域之间差距的一种方法(见图)。

Cadence 设计系统![]() 混合信号仿真的模型和仿真精度与性能和容量的关系。

混合信号仿真的模型和仿真精度与性能和容量的关系。

这些模型使工程师能够使用数字工具仿真模拟行为,从而显著提高仿真速度和容量。最重要的一点是,这些模型都是基于 SystemVerilog 的。因此,RNM 模型可用于在统一的仿真环境中验证和确认模拟、数字和光学组件。

通过简化仿真过程,RMN 帮助工程师以更高的速度和可靠性验证复杂的混合信号系统。

当在 SPICE 或 Verilog-A 中创建的模拟模型不足以应对需要集成光子元件、模拟电路和数字控制器的混合信号仿真时,RNM 特别有价值。通过在数字验证工作流程中实现高速仿真,RNM 有助于消除与传统模拟和数字混合信号协同仿真相关的瓶颈。

EDA 在硅光子学中不断发展的作用

EDA 公司一直在推出一类新型数字混合信号 (DMS) 仿真工具,以帮助降低集成光学元件和电子元件的复杂性。

例如,Cadence Xcelium 数字仿真器完全支持 RNM,支持集成光子域和电域的混合信号仿真。它的与众不同之处在于速度 — DMS 模拟的运行速度明显快于传统的 AMS 模拟。同时,它保持了对整个多晶粒系统进行建模的能力。

Cadence 还开发了一个名为 PhotoNet 的库,使工程师能够访问参数化的 RNM,其中包括最常见的硅光子元件,例如激光器、探测器、波导、合路器和分路器。新库可以与该公司的 EENet 库一起使用,该库包含参数化的 RNM 模型,代表电阻器、电感器和电容器器件,以及二极管、晶体管、运算放大器和其他模拟功能。

使用 PhotoNet,工程师可以仿真硅光子学的功能,并验证其与数字控制器和模拟组件的集成。PhotoNet 模型允许工程师验证光波导和调制器在特定电压条件下是否按预期工作。与 EENet 相结合,这种方法可以更有效地验证混合信号多晶粒系统,减少设计迭代并加快上市时间。

Cadence 还推出了快速采用工具包 (RAK),提供参考代码,向工程师展示如何在同一系统中对电气、光学和数字组件进行建模,然后验证所有组件是否协同工作。

这些工具在克服设计和验证包含硅光子元件的多晶粒系统的挑战方面发挥着关键作用。DMS 可以通过在电气、光学和数字域中实现精确建模,帮助验证和确认未来应用所需的高带宽系统。因此,工程师可以自信地设计和验证下一代高性能系统,满足数据中心、电信、HPC 和 AI 等市场不断变化的需求。

赌注只会越来越高。新的架构方法有望将硅光子学推向新的计算角色。例如,研究人员开发了一种完全集成的光子张量核心,突出了片上光学矩阵作的潜力。随着硅光子学越来越多地与数字逻辑协同设计,DMS 和其他协同仿真工具可能至关重要,使工程师能够在制造芯片之前仿真信号在电气、光学和数字域中的行为。

评论