薄膜3D模拟IC:堆叠式 IC 可在更小尺寸中降低成本并提高性能

尽管数字技术不断进步到商业、工业和休闲活动的各个领域,但模拟集成电路 (IC) 在全球半导体市场上仍占有一席之地。今年,收入预计将达到 850 亿美元,相当于 10% 的年复合增长率。推动这一需求的是人工智能、物联网技术和自动驾驶汽车的进步,所有这些都依赖于模拟 IC 来实现传感和电源管理等功能。与仅处理二进制信号的数字 IC 不同,模拟 IC 可以处理温度和声音等连续信号,因此它们对于与物理环境连接至关重要。

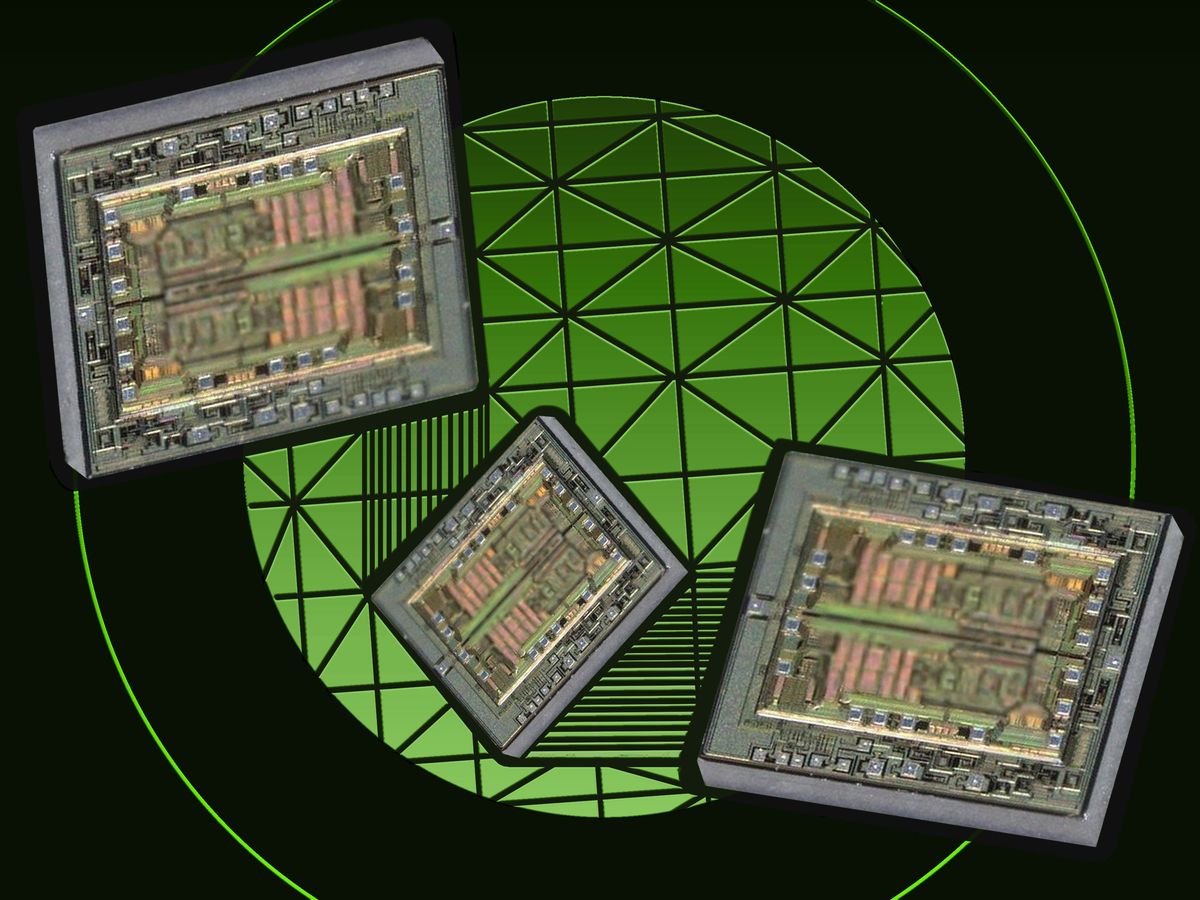

本文引用地址:https://www.eepw.com.cn/article/202503/467747.htm着眼于这一不断扩大的市场,两家总部位于东京的公司 Oki Electric Industry Co. 和 Nisshinbo Micro Devices 合作开发薄膜模拟 IC。这些 IC 还可以垂直堆叠,两家公司声称这提高了电子产品小型化和一次集成更多 IC 的努力。 该技术还通过在更小的空间内实现更多功能或提高性能来降低成本并增加功能。

“我们生活在一个由声音、光线、温度和压力组成的模拟世界,”Nisshinbo 生产工程助理经理 Toshihiro Ogata 说。模拟 IC 将物理世界和数字世界连接起来,处理连续的物理信号,例如自动驾驶汽车中的摄像头和激光雷达检测到的光线和距离,并将其转换为数字数据以支持安全驾驶。

薄膜 3D 模拟 IC 开发

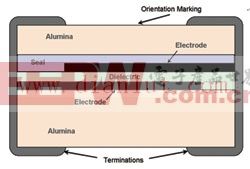

薄膜 3D 模拟 IC 的开发涉及OKI 的晶体薄膜键合 (CFB) 工艺,该工艺将模拟 IC 的功能薄膜层从衬底上剥离出来。(具体过程是商业机密。然后将分离的层粘合到另一个由绝缘层(如氧化硅)隔开的模拟薄膜层上。键合是通过分子之间的吸引力完成的,这种现象称为分子间键合。传统的引线键合以电气方式连接堆叠层。

“与我们的 CFB 堆叠相比,标准堆叠工艺通常使用 TSV [通过硅通孔,一种连接堆叠芯片的垂直布线方法],并涉及先进的加工和特殊设备,”冲电气 CFB 开发部总经理 Kenichi Tanigawa 说。他说,使用 TSV 连接的堆栈中单个芯片的厚度从几十微米到几百微米不等。“然而,在 CFB 堆栈中,每个芯片的厚度只有 5 到 10 [微米],这就是为什么可以在广泛使用的遗留系统上使用低成本的传统半导体光刻技术重新布线的原因。”

CFB 堆叠还支持使用多种不同的 3D 集成方法。一个简单而聪明的工艺使用相同的 IC 设计,其中布线焊盘沿一个边缘排列。在第一层铺设完毕后,每个后续 IC 层的尺寸略微减小并旋转 90 度,使前一层的焊盘暴露在外。这种方法可用于连接多达四层 IC。

然而,由于堆叠模拟 IC 非常薄,层之间会发生串扰,这可能会导致 IC 的信号干扰、噪声和性能下降。这就是 Nisshinbo 凭借其专有屏蔽技术介入的地方。

“我们使用铝作为使用传统半导体工艺铺设的屏蔽材料,”Nisshinbo 的 Ogata 说。他解释说,如果电路层的整个区域都被屏蔽,“它会产生一个大的寄生电容”,指的是电路层之间发生的不必要的电荷存储,这可能会干扰电路运行。“这是因为,与工作电压低于 5 伏的数字 IC 不同,模拟 IC 可处理高达 20 或 30 伏的电压,这会增加寄生电容。”

为了防止这种情况,屏蔽仅适用于堆叠芯片之间发生干扰的关键区域,这些区域是 Nisshinbo 根据其数十年对模拟 IC 的研究和工作确定的。Ogata 说,这种定位减少了信号干扰,而不会影响电路功能。

Chiplet 集成的优势

两家公司指出,薄膜 3D 模拟 IC 堆叠也可用于模拟和数字 IC 组合的情况。这将使它们能够用于小芯片,即可以组合以创建更复杂的器件的模块化 IC。

“与大型单片器件相比,小芯片具有几个优势,”Ogata 说。不是将所有功能都塞进一个大芯片中,而是单独处理传感、处理和电源管理等不同功能。每个小芯片都可以针对其特定功能进行优化,从而降低成本。堆叠小芯片还降低了空间要求,从而实现了更小的器件。而且制造产量可能会更高,因为如果一个小芯片出现缺陷,则可以在组装之前识别并更换小芯片。(而一个大芯片的缺陷意味着必须丢弃整个芯片。

尽管如此,在这种先进的集成成为现实之前,这些公司可能会面临一些挑战。

“小芯片方法对于下一代半导体制造非常重要,”蒙特利尔麦吉尔大学计算机和电气工程教授 Gordon Roberts 说。虽然今天的小芯片已经允许某些组件(如 CPU、GPU 和内存)混合和匹配,但半导体发展的下一步将看到更多样化的组件,如模拟、电源和光学芯片,使用创新的堆叠和互连技术无缝集成。

“能够使用一种可以廉价地组装混合组件袋的工艺将是朝着正确方向迈出的一步,”Roberts 说。“然而,由于该工艺使用减薄的半导体器件堆叠在公共衬底上,因此减薄步骤会引入制造缺陷。”除了威胁制造良率外,裂纹等缺陷还可能在测试过程中滑落,从而导致可靠性问题。“因此,需要确定公司如何处理单个模具并将它们打包在一起,”Roberts 说。

冲电气 (OKI) 和日清纺 (Nisshinbo) 相信他们可以克服这些问题,并且已经计划将他们的新方法用于商业应用。

“将我们的技术应用于小芯片技术意味着我们将能够提供一系列不同的模拟 IC”,OKI 的 Tanigawa 说。“各种数字、模拟、光学和其他半导体器件的异构集成将有助于引领未来新型半导体芯片的开发。”他补充说,两家公司已经开始基于他们的技术开发新产品,并计划到 2026 年实现大规模生产。

评论