延续摩尔定律:先进封装进入3D堆叠CPU/GPU时代

随着 AIGC、8K、AR/MR 等应用的不断发展,3D IC 堆叠和 chiplet 异构集成已成为满足未来高性能计算需求、延续摩尔定律的主要解决方案。

本文引用地址:https://www.eepw.com.cn/article/202309/450404.htm台积电、英特尔等大厂近年来不断加大对异构集成制造及相关研发的投入。此外,领先的 EDA 公司 Cadence 在行业中处于领先地位,推出了「Integrity 3D-IC」平台,这是一个集设计规划、实现和系统分析仿真工具为一体的集成解决方案,标志着向 3D 芯片堆叠迈出了重要一步。

2.5D 和 3D 封装之间的差异

2.5D 和 3D 封装技术的主要区别在于堆叠方式。

2.5D 封装,所有芯片和被动元器件均在基板平面上方,至少有部分芯片和被动元器件安装在中介层上(Interposer),在基板平面的上方有中介层的布线和过孔,在下方有基板的布线和过孔。2.5D 是特指采用了中介层进行高密度 I/O 互连的封装,其特点是多 Die 集成和高密度性。中介层目前多采用硅材料,利用其成熟的工艺和高密度互连的特性。

3D 封装和 2.5D 封装的主要区别在于 2.5D 封装是在中介层上进行布线和打孔,而 3D 封装是直接在芯片上打孔和布线,电气连接上下层芯片。所有芯片和被动元器件器件均位于基板平面上方,芯片堆叠在一起,在基板平面的上方有穿过芯片的硅通孔(TSV),在基板平面的下方有基板的布线和过孔。

3D Chiplet,这个概念应该是 AMD 在 2021 年 6 月份首先提出来的,应用在其 3D V-Cache 上,将包含有 64MB L3 Cache 的 chiplet 以 3D 堆叠的形式与处理器封装在了一起。

从结构上来讲,3D Chiplet 就是将 Chiplet 通过 3D TSV 集成在一起。另外,为了提高互连密度,3D Chiplet 采用了 no Bump 的垂直互连结构,因此其互连密度更高。

AMD 的 3D Chiplet 工艺的实现是由 TSMC 代工的,TSMC 称之为 SoIC,属于其 3D Fabric 的产品范畴,其鲜明的特点就是采用了 no Bump 的高密度垂直互连结构,参看下图。

CPU 和 HBM 堆叠需求

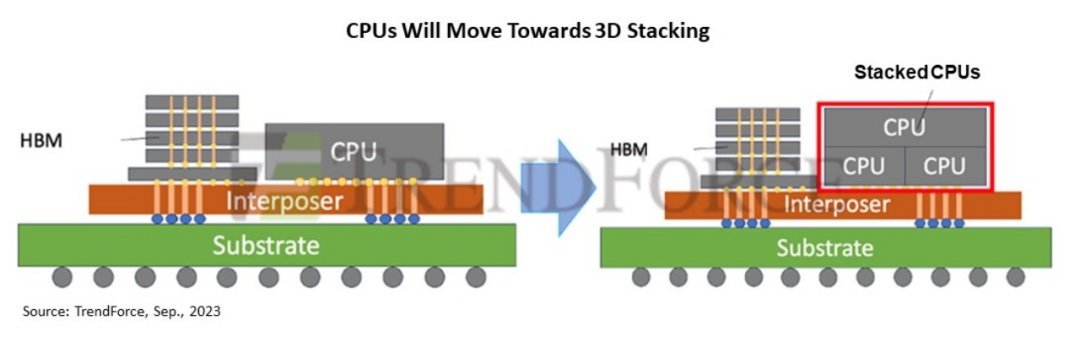

随着 AIGC、AR/VR、8K 等应用的快速发展,预计将产生大量的计算需求,特别是对能够在短时间内处理大数据的并行计算系统的需求。为了克服 DDR SDRAM 的带宽限制,进一步提升并行计算性能,业界越来越多地采用高带宽内存(HBM)。这一趋势导致了从传统的「CPU+内存(如 DDR4)」架构向「芯片+HBM 堆叠」2.5D 架构的转变。随着计算需求的不断增长,未来可能会通过 3D 堆叠实现 CPU、GPU 或 SoC 的集成。

HBM 3D 堆叠盛行,但 CPU 堆叠落后

HBM 于 2013 年推出,作为高性能 SDRAM 的 3D 堆叠架构。随着时间的推移,多层 HBM 的堆叠在封装中已经变得普遍,而 CPU/GPU 的堆叠却没有看到重大进展。

造成这种差异的主要原因可归因于三个因素:1. 热传导,2. 热应力,3. IC 设计。首先,3D 堆叠历来在热传导方面表现不佳,这就是它主要用于内存堆叠的原因,因为内存操作产生的热量比逻辑操作少得多。因此,当前存储器堆叠产品所面临的热传导问题在很大程度上可以被忽略。

其次,热应力问题是由材料之间的热膨胀系数 (CTE) 不匹配以及因芯片减薄和引入金属层而引入的应力引起的。堆叠结构中复杂的应力分布对产品的可靠性具有显著的负面影响。

最后,IC 设计面临 EDA 工具缺乏的挑战,因为传统 CAD 工具不足以处理 3D 设计规则。开发人员必须创建自己的工具来满足工艺要求,而 3D 封装的复杂设计进一步增加了设计、制造和测试成本。

EDA 公司如何提供解决方案

Cadence 在 LIVE 中国台湾 2023 年用户年会上强调了其多年来在开发解决方案方面的努力。他们推出了 Clarity 3D 解算器、Celsius 热解算器以及 Sigrity Signal and Power Integrity 等工具,可以解决热传导和热应力模拟问题。当与 Cadence 的综合 EDA 工具相结合时,这些产品有助于「Integrity 3D-IC」平台的发展,有助于 3D IC 设计的开发。

「3D IC」代表了半导体开发的关键设计趋势。然而,它比其他项目面临更大的挑战和复杂性。除了逻辑 IC 设计中的挑战之外,还需要模拟和多物理场仿真。因此,跨平台的设计工具是必不可少的。EDA 领导者 Cadence 提供的工具有望增强 3D IC 设计工具平台,降低堆叠 CPU、GPU 或 SoC 的技术障碍,从而增强芯片计算性能。

评论