效率最好的内存测试电路开发环境

4.9 模拟

本文引用地址:https://www.eepw.com.cn/article/201702/343955.htm4.9.1 BIST电路仿真

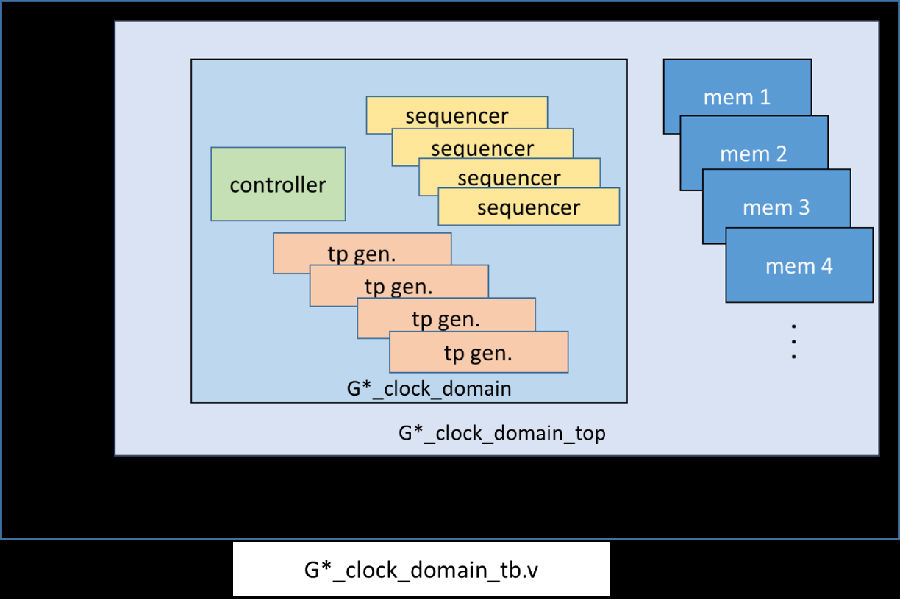

图4-11为BIST电路仿真架构图。此仿真环境使用make语言来建立。使用者可参考mbist文件夹下的Makefile.G*_clock_domain 档案,该档案包含了仿真指令及相关参数。如果使用者想储存相关模拟波形,则可开启G*_clock_domain.f 档案中相关选项。

在mbist文件夹中,使用者可看到不用clock domain有其相关输出档案。在example case中, G1_clock_domain开头的相关档案,为G1 clock domain。除此之外,还有另外两个不同之clock domain。执行仿真的指令如下:

unix% cd multi_lab/top_down_lab/mbist

unix% make G1_clock_domain FUNC=tb

unix% make G2_clock_domain FUNC=tb

unix% make G3_clock_domain FUNC=tb

Note: 如果使用者的design中有使用ROM memory的话,请在执行模拟前,确认相关rom code档案路径正确。

图4-11. BIST电路仿真架构图

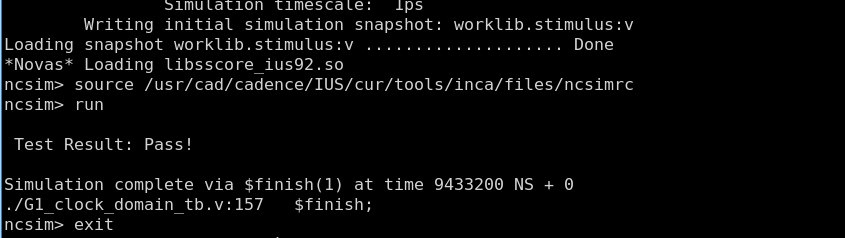

图4-12. G1_clock_domain BIST电路仿真结果

4.9.2 整入BIST电路之仿真

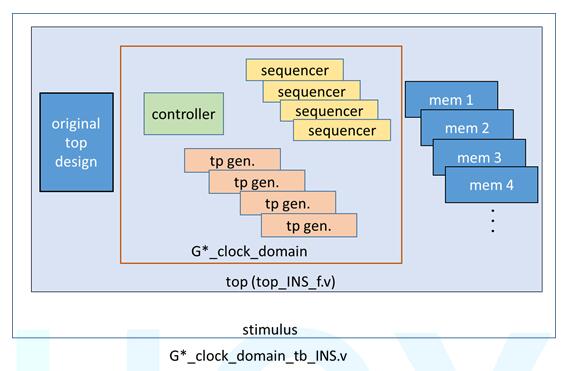

图4-13为整入BIST电路之仿真架构图. 该仿真对象为整合BIST电路后的系统design。此仿真环境使用make语言来建立。使用者可参考mbist 文件夹下的Makefile.G*_clock_domain 档案,该档案包含了仿真指令及相关参数。如果使用者想储存相关模拟波形,则可开启G*_clock_domain_INS_FAULT.f 档案中相关选项。

在mbist 文件夹中,使用者可看到不用clock domain有其相关输出档案。在example case中, G1_clock_domain开头的相关档案,为G1 clock domain。除此之外,还有另外两个不同之clock domain。执行仿真的指令如下:

unix% cd multi_lab/top_down_lab/mbist

unix% make G1_clock_domain FUNC=tb_INS

unix% make G2_clock_domain FUNC=tb_INS

unix% make G3_clock_domain FUNC=tb_INS

图4-13. 整入BIST电路之仿真架构图

图4-14. G1_clock_domain 整入BIST电路之仿真结果

4.9.3 使用Fault Memory Models来模拟

Brains 提供 fault memory models 来验证BIST 电路的正确性。此fault memory models 为执行Brains时自动产生, 使用者可在 FAULT_MEMORY 文件夹中找到这些档案。

用户可透过下列指令来执行相关仿真动作:

执行BIST电路仿真时:

unix% make G1_clock_domian FUNC=tb_f

执行整入BIST电路之仿真时:

unix% make G1_clock_domain FUNC=tb_INS_f

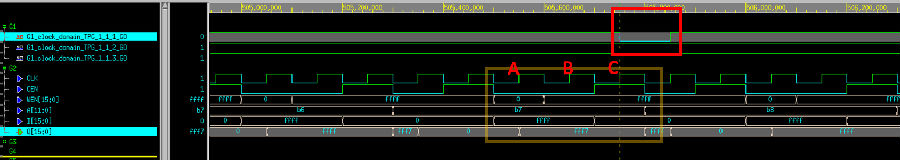

当执行faulty memory模拟时,使用者会得到failed的模拟结果。这是因为faulty memory model中有预先埋入error bit所致。使用者可透过观察波形图来了解此现象。图4-15为一fault memory models仿真的范例波形图。在此范例中,用户可发现关于group G1_clock_domain (1_1_1, sram_sp_4096x16 memory model) 的存取顺序。

A. Write access with data 16’hffff to address 12’hb7

B. Read access from address 12’hb7

C. Read data is 16’hfff7

由于读取的结果和写入的结果不一致,所以导致模拟failed。

图4-15. Fault Memory Models模拟波形图

使用者可在fault memory models中发现预先埋入之error bit信息。图4-16为sram_sp_4096x16 memory model 的error bit范例。

图4-16. Error Bits定义范例

4.10 合成

Brains亦提供BIST电路相关合成script 供用户执行合成工作。该script名称为[design_name].tcl。在执行合成工作前,使用者需先设定相对应standard cell library。如果使用者的design中包含多个clock domain,则需针对各个clock domain执行合成工作。合成的指令如下:

unix% cd multi_lab/top_down_lab/mbist

unix% make G1_clock_domain FUNC=dc

unix% make G2_clock_domain FUNC=dc

unix% make G3_clock_domain FUNC=dc

合成相关报告(面积,timing…等),则会输出在REPORT文件夹中。

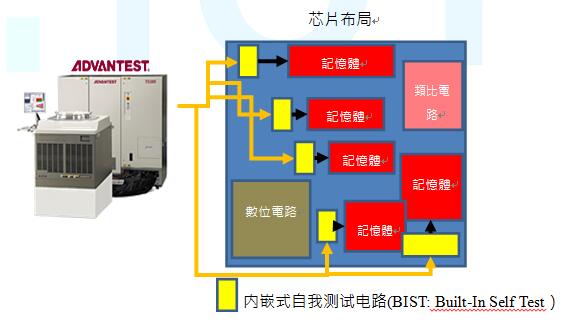

5. 整合流程 (Integrator Flow)

当BIST电路产生完成后,Brains提供另一整合流程 - Integrator flow,供用户将所产生的BIST电路做芯片端整合。该流程主要目的如下列:

n 整合多个BIST controller: Brains所产生的BIST电路架构中,不同的clock domain会有其相对应之BIST controller。用户可透过此流程,整合多个controller接口,整合完后,只需一个IEEE 1149.1接口,即可控制所有BIST controller。

n Hookup pin工作: 使用者design端若有share pin架构时,则可透过hookup pin,将BIST电路相关脚位,与芯片端IO脚位连接。

n 设定芯片初始顺序: 此功能主要用来设定驱动芯片工作时,所需要的相关顺序。包含:切换到BIST模式,clock讯号和reset讯号初始设定…等。

此流程需透过设定BII档案来完成。以下章节将介绍相关流程动作。

5.1 产生并设定BII档案

用户可透过下列指令,来产生BII档案范例。

unix% cd multi_lab/top_down_lab

unix% brains --tempgen

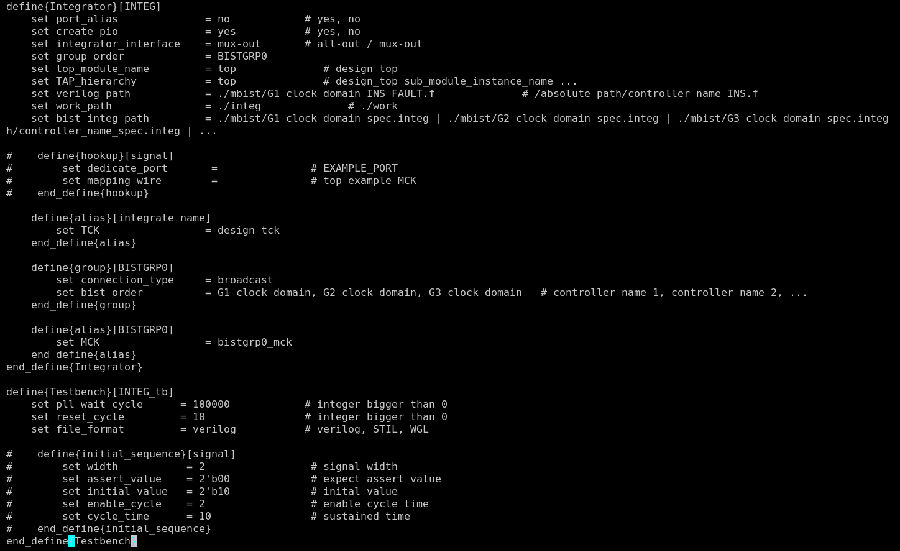

执行上述指令后,选择第一个选项,即可产生BII范例档案 - brains_template.bii。根据example case,使用者需修改BII档案内容如下:

n define{Integrator}[integrator_name] : modified integrator_name to INTEG.

n set top_module_name : top

n set TAP_hierarchy : top

n set verilog_path : ./mbist/G1_clock_domain_INS_FAULT.f

n set work_path : ./integ

n set bist_integ_path : ./mbist/G1_clock_domain_spec.integ |

./mbist/G2_clock_domain_spec.integ |

./mbist/G3_clock_domain_spec.integ

n define {group}

n set bist_order : G1_clock_domain, G2_clock_domain, G3_clock_domian

n define{Testbench}[bench_name] : modified bench_name to INTEG_tb.

n define{hookup}[signal] : comment this functional block

n define{initial_sequence}[signal] : comment this functional block

图5-1为BII 范例档案,用户亦可参考reference 文件夹。

图5-1. BII 档案范例

5.2 执行 Integrator Flow

当BII 档案设定完成后,用户可透过下列指令来执行integrator flow。

unix% cd multi_lab/top_down_lab

unix% brains --integrator -bii brains_template.bii

图5-2. Integrator Flow 执行信息

5.3 Integrator Flow中的模拟工作

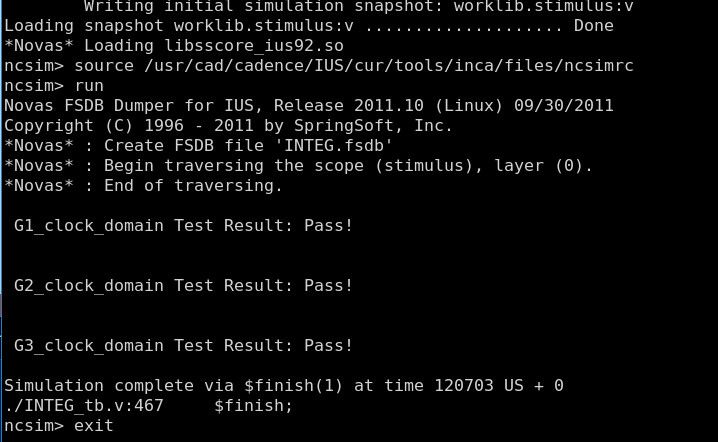

当integrator flow 执行完毕时,Brains会产生相对应之整合后design档案及模拟testbench。用户可执行下列指令来完成仿真工作。图5-3为 integrator flow之模拟结果。

unix% cd multi_lab/top_down_lab/integ

unix% ncverilog INTEG_tb.v -f INTEG_INS.f +nc64bits

图5-3. Integrator Flow模拟结果

评论