用于电池测试和化成的双向同步PWM控制器

本文引用地址:https://www.eepw.com.cn/article/201609/310241.htm

工作原理

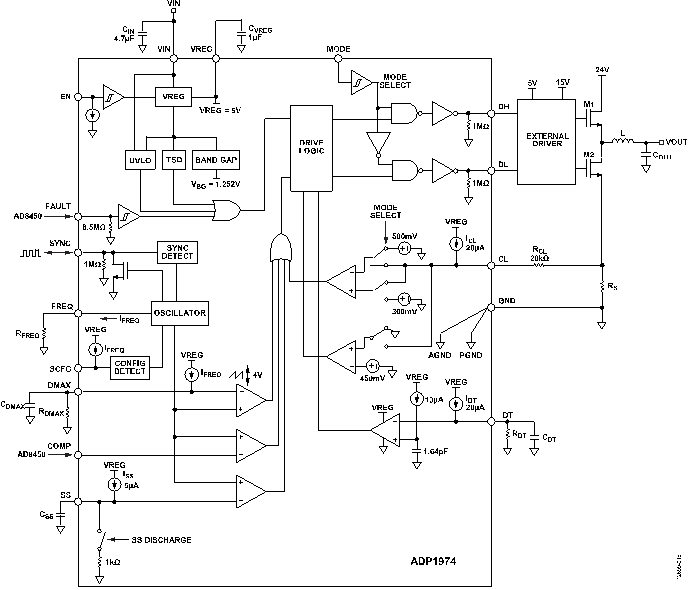

图20. 内部框图

ADP1974是一款恒定频率、电压模式、同步、PWM控制器,用于DC-DC双向应用。ADP1974设计用于配合外部高压FET半桥驱动器(如ADuM7223)和外部误差放大器AFE器件(如AD8450/AD8451)使用,以实现电池测试、充电和放电系统。ADP1974具有高输入电压范围、多个外部编程的控制引脚并集成安全特性。在降压模式下,该器件给电池充电,将电能从输入电源输送到输出。在升压模式下,该器件给电池放电,将电能从电池输送到输入。上述两种情况下,ADP1974均作为同步控制器工作以实现最大效率。

电源引脚

ADP1974有两个电压源引脚:VIN和VREG。 VIN引脚采用6 V到60 V的外部电源工作,是ADP1974内部线性稳压器的电源电压。利用4.7 μF或更大的陶瓷电容将VIN引脚旁路至地。

VREG引脚是内部线性稳压器的输出。 内部稳压器产生5 V(典型值)供电轨,其既可用在器件内部以偏置控制电路,也可用在外部作为MODE、SYNC、DMAX和FAULT引脚的上拉电压。 利用1 μF陶瓷电容将VREG引脚旁路至地。当EN为低电平时,VREG禁用;只要VIN高于内部UVLO(典型值为5.71 V)且EN为高电平,VREG便有效。

采用50 V以上的输入电压工作时,建议增加输入滤波。图21给出了推荐的滤波器配置。

图21. 输入电压大于50 V时的推荐滤波器配置

EN/关断

EN输入用于启动或关闭ADP1974,并且可以采用最高60 V的电压工作。 EN引脚具有精密使能控制功能。当EN电压小于1.22 V(典型值)时,ADP1974关断,VREG禁用,DL和DH均变为低电平。 当ADP1974关断时,VIN电源电流为15 μA(典型值)。 当EN电压大于1.25 V(典型值)时,ADP1974使能,VREG以斜坡方式变为5 V。

除EN引脚外,该器件还可以通过内部TSD事件指示的故障条件、VIN上的UVLO条件或FAULT引脚指示的外部故障条件禁用。工作模式从降压变为升压时,需要禁用器件。

欠压闭锁(UVLO)

当输入电压低于额定工作范围时,UVLO功能防止IC开启,以免进入不良工作模式。当VIN上升时,UVLO不允许ADP1974开启,除非VIN大于5.71 V(典型值)。当VIN降至5.34 V(典型值)以下时,UVLO禁用器件。UVLO电平具有约370 mV的迟滞,当VIN引脚上的电压斜坡较慢时,该迟滞可以防止系统不停地开启和关闭。

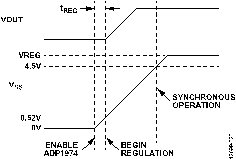

软启动

ADP1974具有可编程软启动功能,可防止启动期间输出电压过冲。 通过EN引脚使能ADP1974时,VREG电压开始上升到5 V。 当VREG达到5 V(典型值)的90%时,5 μA(典型值)内部软启动电流(ISS)开始给软启动电容(CSS)充电,致使SS引脚电压(VSS)上升。

当VSS小于0.52 V(典型值)时,ADP1974开关控制保持禁用。当VSS达到0.52 V(典型值)时,开关使能。随着CSS继续充电且VSS上升,PWM占空比逐渐提高,输出电压得以线性上升。CSS继续充电,VSS上升到内部VREG电压(5 V典型值)。 当COMP设置的系统占空比小于软启动占空比时,外部控制环路接管ADP1974。软启动图参见图22。

当器件关断或检测到故障时,SS引脚的内部1 kΩ有源下拉电阻给CSS放电。

图22. 软启动图

MODE引脚控制ADP1974占空比发生器,在软启动期间会影响DL和DH信号。在降压模式下,DH脉冲启动导通时间(或第一阶段)。在升压模式下,DL脉冲启动导通时间。有关降压和升压操作的更多信息,请参见“工作模式”部分。软启动期间,ADP1974工作在异步模式,不驱动同步FET。在关闭周期中,与低端FET(降压模式)或高端FET(升压模式)并联的二极管导通电流,直至它达到0或下一周期开始。软启动周期完成之后(SS > 4.5 V),ADP1974切换到完全同步模式。

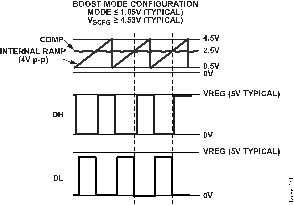

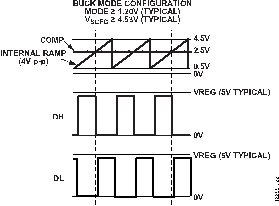

工作模式

ADP1974用作同步降压或升压控制器。当MODE引脚被驱动到高电平——高于1.20 V(典型值)阈值时,ADP1974以降压配置工作,给电池充电。当MODE引脚被驱动到低电平——低于1.05 V(典型值)阈值时,ADP1974以升压配置工作。升压配置适合于电池化成应用中的放电情形。各种模式下ADP1974的表现参见图23和图24。当使能ADP1974时,连接到VREG引脚的内部稳压器也会上电。在VREG上升沿,MODE引脚的状态被锁存,防止工作模式在器件使能时改变。要在升压和降压工作模式之间改变,应关断或禁用ADP1974,调整MODE引脚以改变工作模式,然后重启系统。

当EN引脚被驱动到低电平、FAULT引脚被驱动到低电平或ADP1974由于TSD事件/UVLO条件而禁用时,可以改变工作模式。在FAULT控制信号的上升沿,MODE引脚的状态被锁存,防止工作模式在器件使能时改变。

图23. 升压配置的驱动信号图

图24. 降压配置的驱动信号图

PWM驱动信号

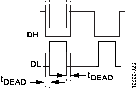

ADP1974有两个5 V逻辑电平输出驱动信号DH和DL,其兼容ADuM7223之类的驱动器。 DH和DL驱动信号同步接通和关断外部驱动器驱动的高端和低端开关。 ADP1974提供电阻可编程的死区时间,以防DH和DL引脚同时跃迁,如图25所示。 在DT引脚与地之间连一个电阻以设置死区时间。

图25. DH和DL跃迁之间的死区时间(tDEAD)

利用DH和DL引脚驱动容性负载时,必须将一个20 Ω电阻与容性负载串联,以降低接地噪声并确保信号完整性。

外部COMP控制

ADP1974 COMP引脚是PWM调制器比较器的输入。ADP1974采用电压模式控制,一个外部误差放大器(AD8450/AD8451)施加于COMP引脚的误差信号与内部4 V p-p三角波形相比较。随着负载改变,误差信号提高或降低。内部PWM比较器通过监控COMP引脚的误差信号和内部4 V p-p斜坡信号,确定适当的占空比驱动信号。随后,内部PWM比较器以所确定的占空比通过DH和DL信号驱动外部栅极驱动器。

COMP引脚的工作电压范围是0 V到5.0 V。 如果VCOMP介于0.5 V到4.5 V,ADP1974将相应地调节DH和DL输出。如果VCOMP大于4.5 V,ADP1974将以编程的最大占空比(或97%,以较低者为准)操作DH和DL输出。如果VCOMP小于0.45 V,ADP1974将根据工作模式以0%占空比操作DH或DL输出,以100%占空比操作互补的DL或DH输出。COMP引脚输入不得超过5.5 V绝对最大额定值。

DL和DH信号摆幅是从VREG(5 V典型值)到地。所用的外部FET驱动器必须具有兼容5 V逻辑信号的输入控制引脚。

峰值限流打嗝实现方案

ADP1974实现了峰值打嗝限流特性,电流通过一个检测电阻在低端FET上测量。 当峰值电感电流超过编程的电流限值并持续500个连续时钟周期(对于100 kHz编程频率,其典型值为5.2 ms)以上时,就会出现峰值打嗝限流情况。如果过流存续时间少于500个连续周期,计数器将复位到0。 发生过流状况时,SS引脚通过1 kΩ电阻放电,驱动信号DL和DH在后续500个时钟周期中禁用,以便FET冷却(打嗝模式)。500个时钟周期到期后,ADP1974通过新的软启动周期重启。

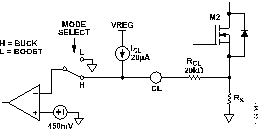

图26显示了峰值限流保护的限流框图。

图26. 峰值限流保护的限流框图

限流阈值系根据所选的模式而在内部设置。 在使用RCL = 20 kΩ(由于有20 μA电流源,其上电压为400 mV)的降压或升压模式下,当RS上的电压达到100 mV时,它就会触发。有关如何设置电流限值的更多信息,参见“应用信息”部分。

负限流检测(降压模式)

ADP1974检测降压模式下电感中的负电流,CL引脚上的比较器设置为450 mV,如图27所示。 当低端FET中的电流降至限值(RS上的-50 mV)以下时,DL驱动器立即禁用,这被用作降压模式下的负电流限值,检测与正峰值电流的一半等效的电流。

图27. 负限流保护框图

PWM频率控制

FREQ、SYNC和SCFG引脚决定ADP1974 PWM控制所用时钟信号的来源、频率和同步。

内部频率控制

ADP1974频率可通过连接在FREQ和地之间的外部电阻来编程。频率设置范围是最小值50 kHz到最大值300 kHz。如果SCFG引脚接VREG,迫使VSCFG ≥ 4.53 V(典型值),或者如果SCFG引脚保持浮空,则SYNC引脚配置为输出,ADP1974以RFREQ设置的频率工作,其从SYNC引脚通过开漏器件输出。SYNC引脚的输出时钟以50%(典型值)占空比工作。 这种配置中,SYNC引脚可将系统中的其他开关稳压器与ADP1974同步。当SYNC引脚配置为输出时,SYNC引脚与外部电源之间需要一个外部上拉电阻。ADP1974的VREG引脚可用作该上拉电阻的外部供电轨。

外部频率控制

当VSCFG ≤ 0.5 V(典型值)时,SYNC引脚配置为输入,ADP1974与施加于SYNC引脚的外部时钟同步,并且ADP1974用作从机。这种同步使得ADP1974能以与系统中其他开关稳压器或器件相同的开关频率和相位工作。ADP1974采用外部时钟工作时,选择RFREQ以提供一个接近于但不等于外部时钟频率的频率,详见“应用信息”部分的说明。

工作频率相移

当施加于SCFG引脚的电压为0.65 V < VSCFG < 4.25 V时,SYNC引脚配置为输入,ADP1974与施加于SYNC引脚的外部时钟的相移版本同步。要调整相移,SCFG和地之间应放置一个电阻(RSCFG)。对于包含多个开关电源的系统,该相移可降低输入电源纹波。

最大占空比

通过DMAX引脚上的外部电阻(连接在DMAX和地之间),可将ADP1974的最大占空比编程为0%到97%的任意值。如果DMAX保持浮空、连接到VREG或编程为大于97%的值,则最大占空比为默认值97%。

外部故障信号

ADP1974配有一个FAULT引脚,当发生外部故障情况时,它会发送信号给ADP1974。外部故障信号停止系统的PWM操作,以免损坏应用和器件。当一个小于1.05 V(典型值)的电压施加于FAULT引脚时,ADP1974即被禁用。 在这种状态下,DL和DH PWM驱动信号均被拉低以防止切换,软启动电容(CSS)通过1 kΩ电阻放电。 当一个大于1.2 V(典型值)的电压施加于FAULT引脚时,ADP1974开始切换。可将0 V至60 V的电压施加于ADP1974的FAULT引脚。

热关断(TSD)

ADP1974有一个TSD保护电路。当ADP1974的结温达到150°C(典型值)时,热关断即触发并禁用切换。在TSD状态下,DL和DH信号被拉低,CSS电容放电至地,VREG保持高电平。当结温降至135°C(典型值)时,ADP1974重启应用控制环路。

应用信息

ADP1974有许多可编程特性,针对具体应用可优化并控制这些特性。ADP1974提供了引脚用于选择工作模式,控制电流限值,选择内部或外部时钟,设置工作频率、工作频率相移、死区时间和最大占空比,以及调整软启动。

降压或升压选择

要使ADP1974以升压(循环)模式工作,应将一个小于1.05 V(典型值)的电压施加于MODE引脚。要使ADP1974以降压(放电)模式工作,应将MODE引脚驱动到大于1.20 V(典型值)的高电平。MODE引脚状态只能在以下情况下改变:通过EN引脚关断ADP1974,或通过FAULT引脚指示的外部故障条件、TSD事件或UVLO条件禁用该器件。

选择RS以设置电流限值

图26显示了峰值限流控制的限流框图。使用下式设置电流限值:

IPK (mA) = 100 mV/RS (2)

其中:

IPK为所需的峰值电流限值(单位为mA)。

RS为用于设置峰值电流限值的检测电阻(单位为Ω)。

当ADP1974配置为降压(充电)工作模式时,内部限流阈值设置为300 mV(典型值),负谷值限流阈值设置为450 mV(典型值)。当ADP1974配置为升压(循环)工作模式时,内部限流阈值设置为500 mV(典型值)。外部电阻(RCL)使电流适当地偏移,以便在降压和升压模式下检测峰值。 RCL值设置为20 kΩ。工作时,设置峰值电流的公式如下:

降压(充电)模式:

VCL (BUCK) = (ICL) × (RCL) − (IPK) × (RS) (3)

VNC (BUCK) = (ICL) × (RCL) + (IVL (NEG)) × (RS) (4)

升压(循环)模式:

VCL (BOOST) = (ICL) × (RCL) + (IPK) × (RS) (5)

其中:

VCL (BUCK) = 300 mV(典型值)。

ICL = 20 μA(典型值)。

RCL = 20 kΩ。

IPK为峰值电感电流。

VNC (BUCK) = 450 mV(典型值)。

IVL (NEG)为谷值电感电流。

VCL (BOOST) = 500 mV(典型值)。

在降压和升压两种工作模式下,ADP1974的峰值电流限值相同。RCL和RS电阻的容差建议为1%或更好。

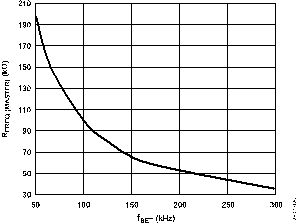

调整工作频率

如果SCFG引脚接VREG,迫使VSCFG ≥ 4.53 V,或者如果SCFG引脚保持浮空且内部连接到VREG,则ADP1974以RFREQ设置的频率工作,SYNC引脚以编程设置的频率输出一个时钟。当VSCFG ≥ 4.53 V时,SYNC引脚的输出时钟可用作需要同步的应用中的主时钟。

如果VSCFG ≤ 0.5 V,则SYNC引脚配置为输入,ADP1974用作从机。作为从机,ADP1974与施加于SYNC引脚的外部时钟同步。如果施加于SCFG引脚的电压为0.65 V < VSCFG < 4.25 V,并且在SCFG和地之间连接一个电阻,则SYNC引脚配置为输入,ADP1974与施加于SYNC引脚的外部时钟的相移版本同步。

无论ADP1974是以主机还是从机工作,都要利用上面的公式精心选择RFREQ。

选择主机的RFREQ

当VSCFG ≥ 4.53 V时,ADP1974用作主机。作为主机,ADP1974以外部RFREQ电阻(连接在FREQ和地之间)设置的频率工作,并且ADP1974在SYNC引脚上输出一个编程频率的时钟。

图28显示了RFREQ (MASTER)值与编程开关频率的关系。

图28. RFREQ (MASTER)与开关频率(fSET)的关系

评论