Xilinx MIG IP核的研究及大容量数据缓冲区的实现

摘要:为了使DDR3 SDRAM更方便、多样地用于工程开发中,本文对XILINX公司DDR3 SDRAM提供的MIG核进行了分析研究,并在此基础上实现了大容量数据缓冲区的逻辑设计。通过对系统中各模块的作用及相互间关系的研究,发现该控制器256位接口对工程开发十分不便,通过创建FIFO控制系统和读写接口FIFO的方式,将接口转换为64位。该方案对控制核重新构建并上板测试,均符合高速数据传输缓存的要求,使DDR3成为一个大容量且可控的高速FIFO。

本文引用地址:https://www.eepw.com.cn/article/201607/294696.htm引言

随着电子行业的飞速发展,人们对于设备处理速度的期望也越来越高。其中,DDR3的出现给整个行业带来了不可限量的跨越,这使得我们在工程中对DDR3更加青睐。DDR3(double-data-rate three synchronous dynamic random access memory)是应用在计算机及电子产品领域的一种高带宽并行数据存储设备,广泛应用于工程设计中。

Xilinx公司为DDR3提供了IP核和方便友好的用户接口,推进了DDR3在FPGA中的使用进程。尤其对于高速数据的传输和处理,FPGA内FIFO远不能满足性能上的要求。这就使得将DDR3设计成大容量数据缓冲区成为工程中的必要需求。然而由于需求的不同,对核接口的要求也会随之改变。Xilinx官方核的接口是256位,但实际需求中64位的居多,本文将从逻辑上对该核进行重建。

1 MIG核的分析及重构

1.1 MIG核的结构

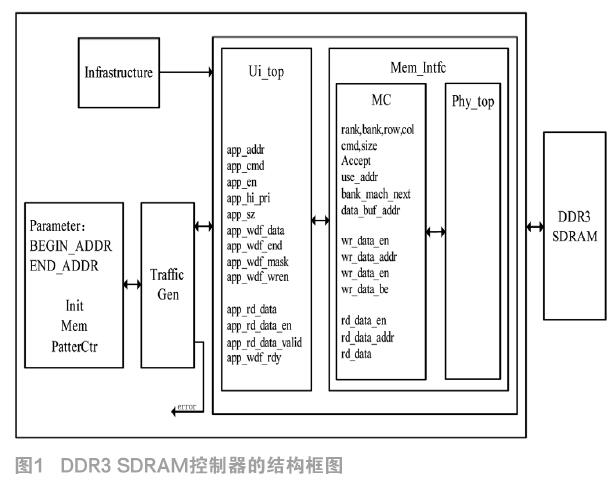

DDR3 SDRAM控制器的主要功能是实现对DDR3 SDRAM存储器的初始化。此外,DDR3 SDRAM控制器还可以将DDR3 SDRAM接口的上下时钟沿数据转变成单时钟沿用户数据,同时还可以产生周期性的刷新指令,完成对DDR3 SDRAM存储器的动态刷新,从而保证数据的完整性。DDR3 SDRAM控制器的结构框图如图1所示,其主要包括四个部分,分别是基础模块(infrastructure)、用户界接口模块(user interface)、物理层模块(physical layer)和存储器控制模块(memory controller)。

基础模块首先接收通过FPGA全局时钟网络的外部200MHz差分时钟,然后通过混合模式,时钟管理器(MMCM)产生用户接口时钟、控制模块使用的时钟以及DDR3存储器的时钟。除此之外,该模块还生成了一个可以全局复位整个DDR3 SDRAM控制器IP核的复位信号。该模块还包括一个延时控制单元,用来同步校准设计中的延时单元,以减少功耗。

用户接口模块的主要功能是连续地输入或输出数据和控制命令,完成对用户数据、控制命令以及地址等信息的接收和缓存,从而实现对数据的缓冲和同步效果。

物理层模块通过物理引脚与片外DDR3 SDRAM直接进行数据通信,它可以对片外DDR3 SDRAM存储器发出的数据进行捕获,同时产生片外DDR3 SDRAM存储器所需要的控制信号,通过缓存把数据、命令以及地址等信号发送给片外DDR3 SDRAM,从而保证了数据信号、命令信号与地址信号的同步。

控制模块的主要功能是实现对DDR3 SDRAM存储器的初始化操作。DDR3 SDRAM上电之后,首先经过200μs的稳定期,然后等到500μs后,把时钟使能信号CKE拉高,保持至少10ns,然后开始ODT过程,对扩展模式寄存器和模式寄存器进行配置,使能DLL并对DLL复位。如果信号phy_initial_done拉高,那么表示DDR3存储器初始化完成,校准结束。初始化结束后,DDR3控制器根据DDR3 SDRAM存储器的用户读写操作时序要求,自动生成所需命令以及控制信号,发送给DDR3 SDRAM存储器。当发送完命令信号之后,给用户发送一个命令应答信号,设计人员可以根据这个命令应答信号判断是否可以发送下一条指令。整个过程中,DDR3控制器自动完成自刷新、激活以及预充电等命令的发送和相应操作的执行,这个过程完全不需要用户干涉DDR3 SDRAM存储器。

1.2 大容量DDR3缓存设计

在本系统设计中,DDR3 SDRAM的主要功能是用于大容量数据缓存,考虑到FPGA不仅处理速度高,而且灵活性和可配置性好,故使用Xilinx公司FPGA提供的DDR3 SDRAM缓存控制器IP核可以轻松实现FPGA与外部存储器之间的接口设计。根据FIFO的基本原理,采用Xilinx公司的FPGA和Micron公司容量为1GB的DDR3内存MT4JSF12864HZ设计实现了一种大容量虚拟FIFO缓存。

该大容量虚拟FIFO缓存设计主要由上行FIFO、FIFO控制器、写接口FIFO、读接口DDR3 SDRAM控制器、时钟模块以及外部的DDR3 SDRAM存储器六部分构成。其整体结构框图如图2所示。DDR3 SDRAM缓存接口的设计主要集中在FPGA内部逻辑设计,具体的设计主要包括DDR3控制器设计、读写FIFO接口设计、FIFO控制器设计以及时钟模块设计。

1.2.1 接口FIFO设计

在该设计中,写FIFO接口和读FIFO接口主要完成数据位宽的转换以及数据的跨时钟域处理;FIFO控制器主要完成对写FIFO接口和读FIFO的控制,按照DDR3控制器用户接口时序对用户接口进行读写操作;DDR3 SDRAM控制器则主要完成对DDR3 SDRAM的初始化,将复杂的读写时序转化为简单的用户读写时序。

写FIFO接口和读FIFO接口主要功能是实现FPGA与DDR3 SDRAM之间的数据传输。由于FPGA与DDR3 SDRAM分别属于不同的时钟域,故在设计中需要采用两个异步FIFO处理数据跨时钟域传输的问题。此外,由于PCI Express总线接口的数据位宽为64位,而DDR3 SDRAM控制器提供的用户接口数据位宽为256位,因此,还需要通过这两个FIFO完成数据位宽的转换。

当信号从一个时钟域传递到另外一个时钟域时,使用异步FIFO可以解决传输过程中出现的亚稳态问题。在ISE 14.2开发平台下设计FIFO的方法有两种,一种是设计者自己设计FIFO的控制逻辑,然后通过CORE Generator生成DPRAM,最后将两者连接起来构成一个FIFO;另一种是利用CORE Generator工具自动生成一个FIFO的IP核,然后在设计中实例化即可使用。第一种方法比较费时,而且有一定的难度,相对而言,第二种方法就简单很多,设计者可以不用关心FIFO实现的细节,而专注于其顶层的功能和应用。本设计直接调用Xilinx公司FPGA内部IP核对FIFO进行设计。

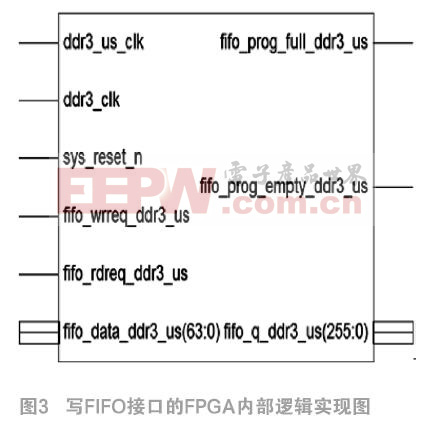

写FIFO接口包含一个异步FIFO和一个同步FIFO,异步FIFO写入数据位宽是64位,读出数据位宽是256位,其写时钟为250MHz的PCI-E系统时钟,读时钟为200MHz的DDR3用户接口时钟;同步FIFO写入和读出数据位宽均为256位,其读写时钟为200MHz的DDR3用户接口时钟。写FIFO接口通过两个FIFO进行级联的方式加深其处理数据的深度。写FIFO接口的FPGA内部逻辑实现如图3所示。

读FIFO接口则只包含一个异步FIFO,其写入数据位宽是256位,读出数据位宽是64位,写时钟为200MHz的DDR3用户接口时钟,读时钟为250MHz的PCI-E系统时钟。读FIFO接口的FPGA内部逻辑实现如图4所示。

1.2.2 FIFO控制器

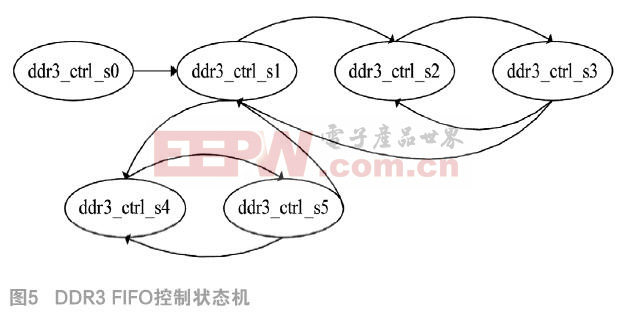

FIFO控制器的主要功能是实现对写FIFO接口、读FIFO接口与DDR3 SDRAM之间数据交互的控制。由于DDR3 SDRAM内存工作时钟频率为400MHz,此时其理论传输带宽为51.2Gbps,远远高于读FIFO接口和写FIFO接口的数据传输带宽,故FIFO控制器需要根据读写FIFO所缓存的数据量,对DDR3 SDRAM总线进行分时复用。DDR3读写控制状态机设计如图5所示。下面就将对各状态含义与跳转条件做简要说明:

ddr3_ctrl_s0:复位或异常情况下,默认等待状态。当DDR3控制器完成初始化后,即phy_init_done有效时,跳转到ddr3_ctrl _s1状态。

ddr3_ctrl _s1:当DDR3内存不满且DDR3写接口的FIFO非空时,如果命令地址FIFO准备好接收命令且写数据FIFO准备好接收数据,则跳转到ddr3_ctrl _s2状态,同时将app_wdf_wren置为有效,将DDR3写FIFO接口的读使能置为有效;当DDR3内存不空且DDR3读接口FIFO不满时,如果命令地址FIFO准备好接收命令,则跳转到ddr3_ctrl _s4状态;其他情况状态不跳转。

ddr3_ctrl _s2:当写入数据FIFO准备好接收数据时,跳转到ddr3_ctrl _s3状态,同时将app_wdf_end置为有效,指示当前是最后一个有效数据,在给出写命令和地址的同时将使能置为有效;其他情况状态不跳转。

ddr3_ctrl _s3:当命令地址FIFO准备好接收命令且写数据FIFO准备好接收数据时,如果写入次数等于32,此时刚好写满一行,则跳转到ddr3_ctrl _s1状态,同时将app_en、app_wdf_wren和DDR3写FIFO接口的读使能置为无效;如果写入次数小于32,即没有写满一行数据,则跳转到ddr3_ctrl_s2状态,同时将app_wdf_wren和DDR3上行FIFO读使能置为有效。当命令地址FIFO没有准备好接收命令但写数据FIFO准备好接收数据时,将app_wdf_wren和DDR3写FIFO接口的读使能置为无效,同时将app_wdf_end置为无效,状态不跳转。

ddr3_ctrl _s4:状态跳转到ddr3_ctrl _s5,在给出读命令和地址的同时将使能置为有效。

ddr3_ctrl _s5:当命令地址FIFO准备好接收命令,如果读出次数等于32,此时刚好读完一行数据,状态跳转到ddr3_ctrl _s1;如果读出次数小于32,即没有读完一行数据,则跳转到ddr3_ctrl_s4状态;其他情况时将app_en置为无效,状态不跳转。

1.2.3 时钟模块设计

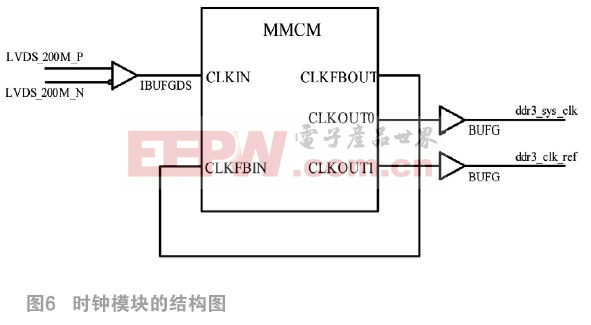

在本系统的时钟模块设计中,时钟模块的具体结构如图6所示。它包括一个IBUFGDS(差分信号输入缓冲)、一个MMCM(混合模式时钟管理器)和两个BUFG(全局时钟输出缓冲)。在进行设计的时候,需要用户提供给DDR3 SDRAM控制器两个时钟,这两个时钟分别是DDR3 SDRAM存储器工作的系统时钟(ddr3_sys_clk)和时延单元的参考时钟(ddr3_clk_ref)。由于DDR3 SDRAM要满足系统的传输带宽要求,设计的时候需要其工作时钟频率为400MHz,因此,DDR3控制器上以工作时钟频率运行的系统时钟频率为400MHz,提供给时延单元的参考时钟频率为200MHz。

考虑到系统提供的是来自全局时钟网络的200MHz差分时钟,但是在DRR3控制器定制的时候,在MIG设置界面选择的时钟输入形式是单端输入,因此,首先需要将输入的全局差分时钟连接到IBUFGDS(差分信号输入缓冲)上,然后再通过一个MMCM倍频出DDR3 SDRAM控制器所需要的两个时钟。该时钟模块的FPGA内部逻辑实现如图7所示。

2 运行和测试

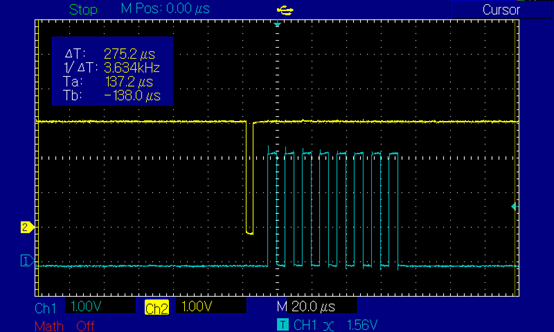

本文测试所选芯片为XILINX V6系列FPGA,所选环境为ISE14.6。在该环境中创建支持DDR3的IP核,根据设计目的对核进行修改。将程序烧写至FPGA后,可通过逻辑分析仪ChipScope来抓取内部想要观察的信号。下图是实时抓取的FIFO数据。

其中fifo_q_ddr3_us是256位的核接口信号,fifo_data_ddr3_us和fifo_data_q_ds分别为改造后的对外接口,均为64位。由上述所抓取的fifo_data_ddr3_us的数据可以看到,数据最先到达该fifo,然后经过缓存进入256位fifo_q_ddr3_us,最后存入DDR3。读出数据是从fifo_data_q_ds输出。测试数据是递增的,由上述信号可以看到,该改造达到了预期目的。

3 结束语

本文通过基于FPGA DDR3 SDRANM IP核的逻辑重构,将256位宽的接口改造为64位接口,使得工程上数据接口更为通用。为后期工程开发提供便捷可控的接口。随着电子行业的飞速发展,对高速大容量缓存的需求也随之增大。怎样利用当前的快速缓存技术于自己的设计中成为开发中的一个门槛。本文正是结合实际需求给出了这一答案。

参考文献:

[1]Virtex-6 FPGA Memory Interface Solutions (UG406). Xilinx Corporation,2010.

[2]夏玉立, 雷宏, 黄瑶.用Xilinx FPGA实现DDR SDRAM控制器[J].微计算机信息. 2007(26).

[3]陈雨, 陈科, 安涛.高速图像处理系统中DDR2-SDRAM接口的设计[J].现代电子技术. 2011,34(12).

[4]任颖, 黄建国.基于FPGA的DDR2 SDRAM控制器接口的简化设计方法及实现[J].电子质量.2008(11):31-33.

[5]Xilinx. Virtex-6 FPGA user guide[R]. USA: Xilinx,2008.

[6]庾志衡, 叶俊明, 邓迪文.基于FPGA与DDR2 SDRAM的大容量异步FIFO缓存设计[J].微型机与应用.2011,30(6).

本文来源于中国科技期刊《电子产品世界》2016年第7期第43页,欢迎您写论文时引用,并注明出处。

评论