基于AD7266的多路2Ms/s同步采样A/D模块的设计

3.2 数据采集、传送及缓存

设计中转换数据的定时关系如表4所示。本文引用地址:https://www.eepw.com.cn/article/194996.htm

最大转换时间TCONVERT为14×TSCLK,在电源5V、时钟32MHz条件下转换时间为437.5ns。精确控制CS*与SCLK的时序,从串行数字接口获得转换后的数据,时序见图4。

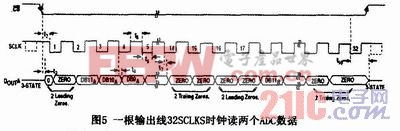

设计中用一根输出线读取两个ADC数据。共需32个时钟脉冲:其中A通道2个零标记头、12位数据、2个零尾标记(计16位);B通道2个零标记头、数据12位、2个零尾标记(计16位)。一根输出线读取两个ADC数据时序的见图5。

3.3 数据接口设计

串行数据在时序控制下输出转换为并行数据送存储器缓存,数据接口为兼容的高速串行接口SPI/QSPI/MICROWIRE/DSP或由CPLD构成的接口。如图2所示,本设计中采用CPLD实现接口的设计。串行数据经串行/并行转换后输出到FIFO进行缓存。

模块的接口为PCI总线,由接口桥电路PCI9052实现。数据可用中断或查询方式进行单组或批传送。PCI9052采用非复用、单周期读/写模式。

3.4 抗干扰设计

为减少高频干扰,在制作电路板时应尽量采用多层板,在中间加上地线层和电源层。另外,由于采样时钟的相位抖动会对AD产生相当于模拟输入正弦波所产生的影响,而时钟输入对AD7266来说相当于一个模拟输入,因此应当尽量选择低抖动晶体振荡器。采用高频时钟经分频后获得需要的时钟信号效果较好,并将时钟电路与系统模拟电路、数字电路相隔离,以防止其产生噪声。数字端电源、模拟端电源、数字端电源地和模拟端电源地增加电容网络,该电容网的作用有三个:其一是与内部参考放大器一起在大频率范围下提供一个低阻抗源以驱动A/D内部电路;其二是提供运放动态需要的补偿;其三是限制由参考电源产生的噪声干扰。

采用直流耦合差分输入的电路。在这种模式下,直流输入将上升到相对参考电压对称摆动的点上。电路把两个放大器配置为一个对称单元以形成差分放大器。放大器的差分驱动电路可以把一个以地为参考电压的单端信号转换为一个以AD的VREF管脚电压为中心的二倍的差分信号。单端输入信号接到不同放大器的两个相反的输入端上可以驱动差分放大器,放大器可选用双通道放大器AD8056。通常为保护AD7266不受过电压的影响,应当在放大器的输出端和AD的输入之间加一个接地二极管。如果放大器和AD7266用同样的正电源,AD就不会受到过电压的影响。这种电路应当是最佳选择,为信号稳定变换提供保障。

4 结束语

本设计充分体现A/D采集模块的特点,整个设计结构紧凑、性能稳定、抗干扰能力强,并且适用于各种工业控制场合。设计上此模块可实现四路一组的高速同步采样及多组2Msps的采样吞吐量。应用DSP高速处理器进行数据处理,可以很容易地实现实时谐波分析功能,且系统运行稳定性和所能达到的精确度均优于传统的以微控制器为核心所构成的系统。

评论