基于AD7266的多路2Ms/s同步采样A/D模块的设计

1.3 AD7266引脚说明

AD7266芯片的引脚说明本文引用地址:https://www.eepw.com.cn/article/194996.htm

2 设计原理

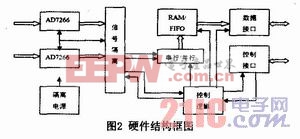

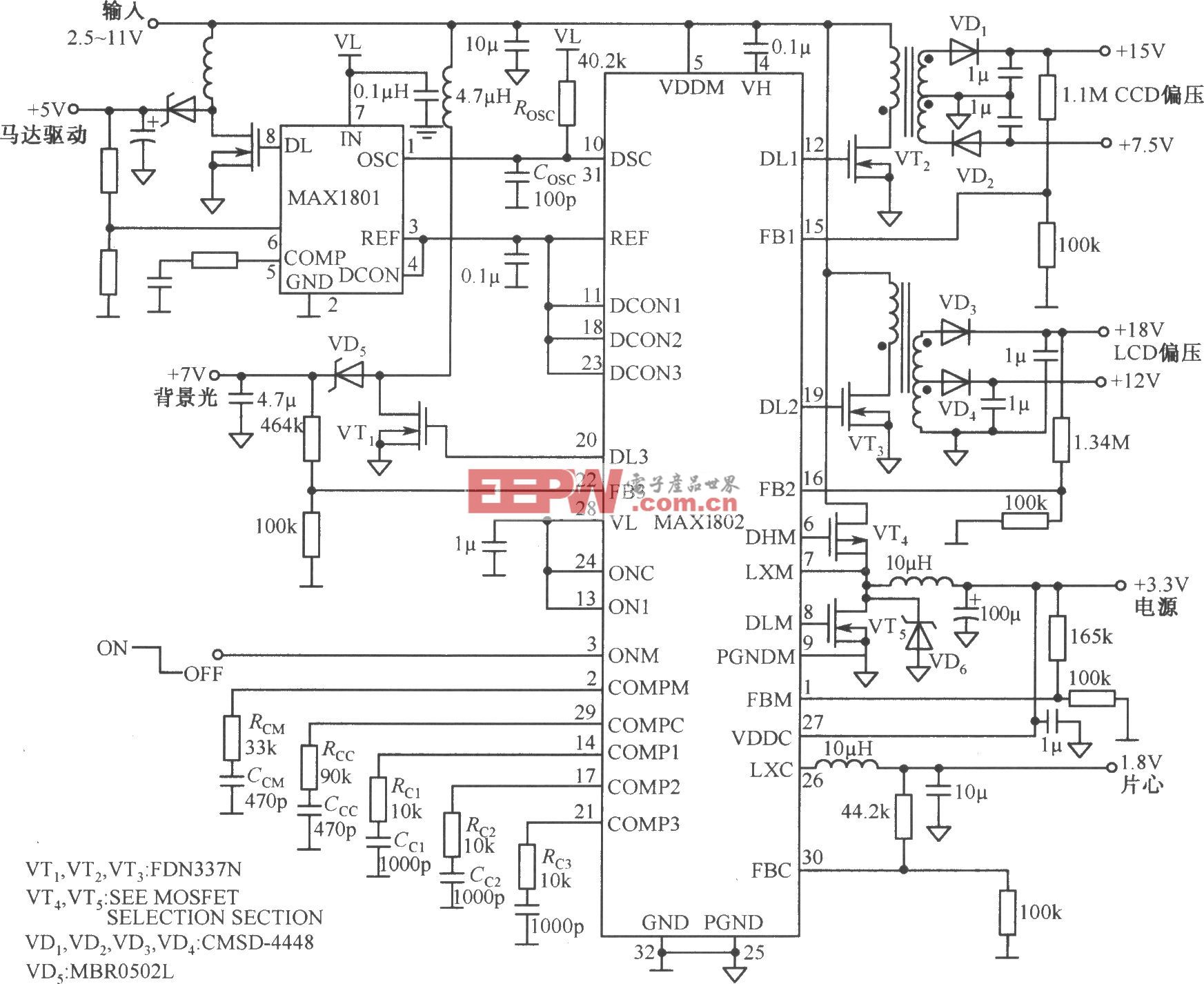

模块主要实现多路数据采样功能,主要用两片AD7266构成24路单端或12路差分输入,其中有四路可同时采样。外围逻辑及接口控制由CPLD、DSP或单片机构成,A/D输出的串行数据变为并行后送入RAM或FIFO缓存。硬件结构框图如图2所示。

3 实现方法

3.1 输入模拟信号预处理

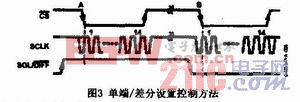

输入模拟信号主要有以下几种:0~5V、0~10V、0~±5V、0~±10V、0~20mA、4~20mA等。AD7266的最大输入电压范围为0~2×VREF即0~5V,电压信号0~5V可用,其它信号需调理变换为0~5V。电流信号用250 Ω电阻取样变为电压信号后供AD7266转换用。电路中两片AD72 66可根据输入信号是单端或差分分别进行设置,设置过程见图3。

图3中通过单端/差分控制信号SGL/DIFF*来实现对单端或差分输入方式的控制,其中SGL/DIFF*高电平为单端输入,SGIdDIFF*低电平为差分输入;CS*下降沿有效。设计中通过控制单端/差分控制信号SGL/DIFF*实现不同输入方式与不同输入范围,具体实现输出二进制码情

况见表2所示。

设计中通过单端/差分控制信号(SGL/DIFF*)与通道选择控制信号(A0~A2)实现模拟输入类型的不同,具体模拟输入类型与通道选择情况见表3所示。

评论