降采样FIR滤波器的设计与硬件实现

结合滤波器的阶数可知式(1)中的h(n)可以表示为:

h(n)=-21×[δ(n)+δ(n-30)]-8l×[δ(n-1)+δ(n-29)]-58×[δ(n-2)+δ(n-29)]+…+6599×δ(n-15). (4)

于是,有:y(n)=-21×[x(n)+x(n-30)]-8l×[x(n-1)+x(n-29)]-58×[x(n-2)+x(n-29)]+…+6599×x(n-15). (5)

将以上各系数用(3)中的拆分结果替换,可将式(5)进一步写为:

y(n)=-(16+4+1) [x(n)+x(n-30)]-(64+16+1) [x(n-1)+x(n-29)]-(64-8+2) [x(n-2)+x(n-29)]+…+(8192-2048+512-64+8-1)・x(n-15). (6)

这样,输出y(n)可表示成输入移位相加减的形式。至此,抗混叠FIR滤波器便告设计完成。

由图2可知,抗混叠滤波器输出信号必须经过降采样才能输出。而对于本设计的滤波器,其降采样率为2:l,理论上把式(6)取出一半即可满足降采样要求,但是,这样就意味着之前浪费了一部分硬件资源去计算这一半不用的数据。基于此考虑,在设计滤波器时可加上一个降采样控制器,x(n)还是正常输入,每一拍进一个新的采样点,而滤波过程则用降采样控制器控制,这样可使计算每隔一拍进行一次。本文引用地址:https://www.eepw.com.cn/article/191625.htm

3 仿真结果分析

3.1 滤波器的幅频响应

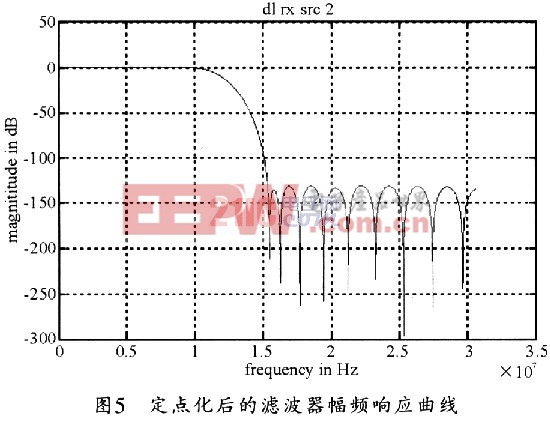

图5所示是在matlab中利用定点化之后的滤波器系数画出滤波器的幅频响应特性曲线。

该曲线与2.1中设计的滤波器幅频曲线基本一致,从而验证了本设计的正确性。

3.2 硬件代码的仿真波形

对于本文中设计的硬件架构,用Verilog语言写出相应的硬件实现代码,再用modelsim软件进行波形仿真,其仿真结果如图6所示。

滤波器相关文章:滤波器原理

滤波器相关文章:滤波器原理

评论