基于FPGA的CAN总线通信接口的设计

2 FPGA逻辑控制程序

2.1 SJA1000逻辑控制

由于SJA1000地址线与数据总线复用,FPGA不仅仅要产生SJA1000读写控制引脚的信号逻辑,还需要模拟单片机等处理器产生对SJA1000的寻址信号,实际上是一个向SJA1000写地址的过程。根据SJA1000技术手册的时序要求,要完成对SJA1000内寄存器的正确读写,接口逻辑必须在地址锁存信号ALE为高电平时将SJA1000的寄存器地址当作数据写入,然后在ALE和片选信号

2.2 SJA1000读写数据流程控制

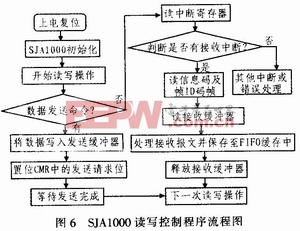

FPGA对SJA1000控制程序包括SJA1000初始化、SJA1000读数据、SJA1000写数据等部分。SJA1000的初始化是在复位模式下进行的,在复位模式下分别设置时钟分频器CDR、总线定时器(BTR0、BTR1)、输出控制寄存器(OCR)等重要寄存器。SJA1000通信波特率由总线定时器决定,需要与后端节点的波特率相同才能进行节点间的正常通信。FPGA上电后需要延时一段时间.等待SJA1000复位完成才能进行SJA1000初始化。初始化仿真波形如图5(a)所示。SJA1000内部有一个接收缓冲器和一个发送缓冲器。FPGA对SJA1000的读写操作,实际上对这两个缓冲器的读写控制。当FPGA接收CAN总线数据时首先读取SJA1000中断寄存器IR判断是否有接收中断。如果有接收中断到来则开始读取缓冲器内的8字节数据,然后释放接收缓冲器(写命令寄存器CMR)。使用Xilinx公司的Chipseope软件进行板上测试,测试数据为(E0,E1,……E7),抓取到的波形如图5(b)所示。FPGA读写SJA1000的流程控制图如图6所示。

评论