基于FPGA的AD7862接口电路设计

2 接口电路程序设计

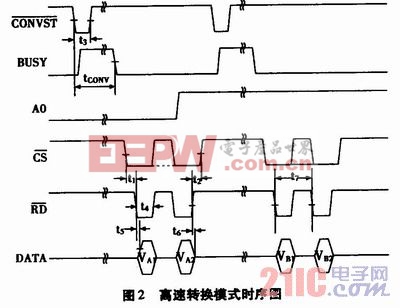

在本设计中用的是AD7862-10,采用高速转换模式,典型转换时序如图2所示。

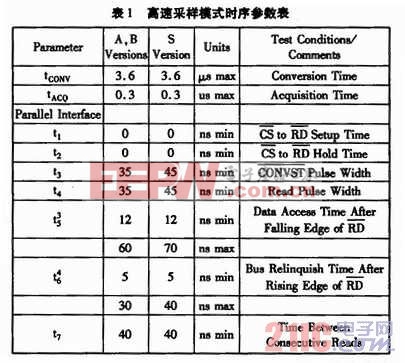

图2中队应的时间参数的要求如下表1所示。

从图2的时序图可以看出AD7862通过输入脉冲信号CONVST启动转换。在CONVST信号的下降沿,片上的两个track/hold都同时的被设置为hold状态,两个通道开始进行转换。转换时钟由内置的晶振提供。BUSY信号指示转换结束,同时两个通道的转换结果可以被读出。由AO的值来决定第一次读取的值是VA1或者VB1,第二次读取的是VA2或者VB2。当CS信号和RD信号为低时,数据被从12位的并行数据线上读取。在高速转换模式下,AD7862的转换时间为3.6 us,track/hold收集时间为0.3 us。为了保证最佳转换效果,在转换期间和下一次转换开始前300 ns不能进行读取操作。

上述的时序图对应为先读取VA1和VA2,然后在读取VB1和VB2,对应的信号AO首先被设为低电平,然后被拉为高电平。在设计驱动电路的过程中,一定要保证设计的时序满足上述时序参数的要求,不然就有可能发生采样不准,出错。

结合AD7862的转换速度,FPGA选择1O MHz的处理时钟。对于整个转换过程的控制用一个状态机来完成,状态机分为12个状态 (idie,convert1,busy1,reada1,wait1,reada2,swapchna1,convert2,busy2,readb1,wait2,readb2),其中idle状态为空闲等待转换状态;convertl指示第一次转换启动状态;busyl指示第一次转换状态;resdal状态下读取 VA1;waitl状态为读取VA1和VA2之间的等待状态;reada2状态下读取VA2;swapchnal状态指示交换到另一个通道进行转换;convert2指示第二次转换启动状态;剩余状态和前面的类似,只不过是针对VB1和VB2而言。设计代码如下(只描述VA1和VA2的部分,剩下的类似):

评论