一种基于FPGA 的嵌入式块SRAM 的设计

A11∶8>_DEC与A7 译码均为低有效,A6译码为高有效。之所以能够用或门译码,是因为没被译码的一对BL 和BLN 位线上的数据是不会被写入存储单元的,如A70>为1,A11∶8>_DEC为1,BL0>与BLN0>均为1,即使字线打开了,它们也是不会被写入存储阵列的。而被译码选中的一对位线,BL与BLN 互补,它们上的数据即可被写入存储单元。

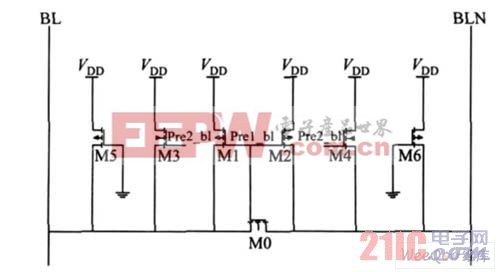

3.2.3 位线充电电路

对位线的充电共有两对充电管和一对上拉管,宽长比在设计上也是有讲究的。上拉管一直开启,为倒比管。栅极接平衡管的M1 和M2 时序要求较高,因为它们的宽长比较大,为主要充电管。在BRAM总使能信号ENA和时钟CLK有效时工作,进行预充电。在CLK 下降沿,M1 和M2 短暂关闭可执行读操作。M1、M2和平衡管都在Pre1_BL信号控制下工作。

Pre1_BL 需在数据线与位线之间的开关管打开时关闭,不影响数据的读操作。Pre1_BL信号受到数据线与位线的开关管控制信号A 的约束,图4 的结构即可避免Pre1_BL与A的时序冲突,在A有效时,Pre1_BL无效,且当A 关闭时,Pre1_BL 延迟开启。

而M3 和M4 管则由Pre2_BL信号控制,Pre2_BL由BRAM全局信号ENA、CLK 和WE 一起控制。由于BRAM 在进行写操作时,也可镜像地输出写入的数据,即也做了读操作。为了更好地在写入时也读出,且满足频率要求,有必要增加这一充电管。

图5 Pre1_BL 信号产生电路

图6 位线充电电路

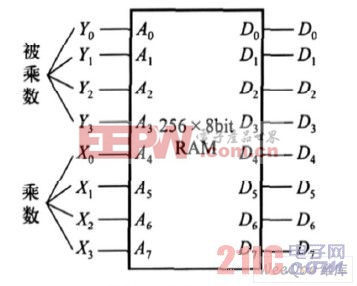

4 BRAM应用

作为随机存取存储器,BRAM 除了实现一般的存储器功能外,还可实现不同数据宽度的存储,且可用作ROM,以实现组合逻辑函数。当初始化了BRAM后,一组地址输入就对应了一组数据的输出,根据数据和地址的对应关系,就能实现一定的函数功能,BRAM 之所以能实现函数逻辑,原因是它拥有足够的存储单元,可以把逻辑函数所有可能的结果预先存入到存储单元中。如实现4 × 4 二进制乘法器:

即由地址来查找数据,如同LUT。在FPGA 中,还可用BRAM来实现FIFO中的存储体模块,CLB实现控制逻辑,设计紧凑,小巧灵活。

图7 4 位乘法器

5 结论

如今系统越来越高级,数字电路也高度集成,存储器也越来越多地应用于嵌入式芯片中。本文设计了一种应用于FPGA 的嵌入式存储器结构,符合一般的双端SRAM 功能,且具有FPGA 功能块的可配置选择,灵活性很高。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论