基于CPLD的信道编解码器的设计与实现

摘要:设计是以信道的编解码的思想,实现信道的编解过程,通过用VHDL语言对Altera公司生产的可编程逻辑器件CPLD进行编程,从而实现HDB3码编解码过程,同时也可采用原理图的形式用CPLD实现卷积码编解码器。通过本次设计,实现了信道的编解码,从而了解信道的编解码过程。

关键词:信道编解码;CPLD;HDB3码;卷积码

0 引言

通过对可编程逻辑器件CPLD用VHDL语言进行编程,实现编码译码过程,本设计采用HDB3码对可编成逻辑器件进行编程。

1 CPLD相关内容及信道编解码

CPLD(Complex Programmable Logic Device)是复杂可编程逻辑器件的简称,它是20世纪90年代初期出现的高密度可编程逻辑器件,采用E2CMOS工艺制作,一般由三种可编程电路组成,即可编程逻辑宏单元,可编程输入/输出单元和可编程内部连线。它可利用EDA技术中的MAX+ PLUS2作为开发工具,将设计的电路图或硬件描述语言编写的程序综合成网表文件写入其中,制成ASIC芯片。CPLD的突出优点是可反复编程,集成度非常高,数据速率快,同时具有较大的灵活性。

2 编码器的VHDL建模与程序设计

2.1 HDB3码编码规则

HDB3码是AMI码的改进型,称为三阶高密度双极性码,它克服了AMI码的长连0串现象。HDB3码的编码规则为先检查消息代码(二进制)的连0串,若没有4个或4个以上连0串,则按照AMI码的编码规则对消息代码进行编码;若出现4个或4个以上连0串,则将每4个连0小段的第4个0变换成与前一非0符号(+1或-1)同极性的V符号,同时保证相邻Y符号的极性交替(即+1记为+V,-1记为-V);接着检查相邻V符号间非0符号的个数是否为偶数,若为偶,则将当前的V符号的前一非0符号后的第1个0变为+B或-B符号,且B的极性与前一非0符号的极性相反,并使后面的非0符号从V符号开始再交替变化。

2.2 HDB3编码器的VHDL建模与程序设计

HDB3码的VHDL建模思想是在消息代码的基础上,依据HDB3编码规则进行插入“V”符号和“B”符号的操作,且用2位二进制代码分别表示。最后完成单极性信号变成双极性信号的转换。其编码模型如图1所示。

2.2.1 插“V”模块的实现

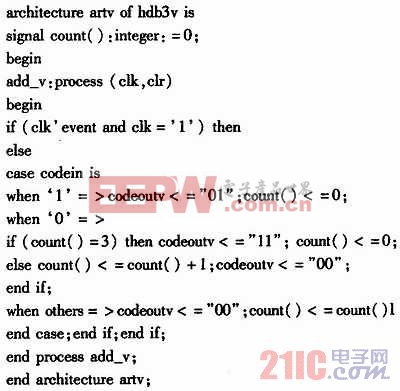

插“V”模块主要是对消息代码里的四连0串的检测,即当出现四个连0串的时候,把第四个“0”变换成符号“V”,用“11”标识。“1”用“01”标识,“0”用“00”标识。实现的VHDL结构代码如arty:

评论