锁相环频率合成器的方案研究

图2为移动通信909~915 MHz频率合成器的设计电路,其中压控振荡器输出的频率通过双模预分频器MC12054A预分频,再输出到可编程并行输入锁相环MC145152中,单片机AT89C51通过I/O口对MC145152进行编程,以改变其计数器的计数初值,从而改变分频比,鉴相器双输出端输出的误差信号φV和φR输入到双端输入的有源低通滤波器,输出信号直接对压控振荡器进行控制,构成了一个完整的数控锁相环。单片机接收人工调整、设置的数值,并对MC145152的计数器计数初值进行不同的预置,以锁定不同的频率,达到改变不同频点信号的目的。

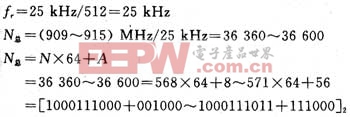

本文引用地址:https://www.eepw.com.cn/article/188997.htm2.1 909~915 MHz频率合成器元件的选取锁相环频率合成器选用芯片MC145152。晶振选用12.8 MHz的温补晶体,他的频率稳定度较高,可达10-8。低通滤波器选用运放芯片MC33171;双模分频器选用MC12011与MC10154串联组成÷64/65双模前置分频器,环路总分频比N总=N×64+A=36 360~36 600,N=568~571,A=0~63。

2.2 909~915 MHz频率合成器电路的设计

(1)MC145152芯片参数的设计

909~915 MHz频率合成器电路图如图2所示。

fVCO=909~915 MHz,P=64,晶体振荡器的频率为12.8 MHz,参考分频器R取512,RA2~RA0为100,则:

因此,N的取值范围为568~571,A的取值范围为0~63,对应分频比36 360,N计数器二进制为1000111011,A计数器二进制为111000,对应分频比36 600,N计数器二进制为1000111011,A计数器二进制为111000,其余类推。R计数器、N计数器、A计数器可预置,各管脚接地为逻辑0,悬空为逻辑1。

2.3外围电路参数设计

假设压控振荡器控制电压△Vd=10 V,鉴相灵敏度Kd=9/2πV/rad,ζ值的大小直接影响环路的瞬态特性,ζ值大,环路的低通特性性能变差,对输入频率成分滤出能力降低;ζ值太小,瞬态特性有较大的过冲,捕捉时间加长,故需折衷考虑ζ的取值,通常比较合适的数值为ζ=0.5~1.5,通常选择最佳值1。

有源比例积分滤波器由运放芯片MC33171构成,根据前面确定的参数K0,Kd和ωn可以确定R1和R2。

取电容标称值C为0.015μF,则R1为1 574 Ω,取电阻标称值1.6 kΩ,R2为53 333 Ω,取标称值5.4 kΩ。

当ζ选定和快捕时间ωn选定以后,自然角频率ts由下式决定:

如还有其他技术指标要求,还需进行实验调整,使之达到指标要求并留有余量,最后再决定频率合成器环路参数。

低通滤波器相关文章:低通滤波器原理

分频器相关文章:分频器原理 尘埃粒子计数器相关文章:尘埃粒子计数器原理 鉴相器相关文章:鉴相器原理 锁相环相关文章:锁相环原理

评论