输电线路行波故障定位中高速数据采集系统的实现

摘 要:为了用单片机实现对变化速度极快、变化过程极短的高速瞬态行波信号进行采样,研究了一种以DS80C320单片机为控制器。结合适当的外围电路和合理的控制逻辑构成的高速同步数据采集系统。阐述了快速寻址的方法、高速A/D转换与快速存储操作的协调控制关系和PC机总线接口技术,此系统符合ISA总线标准,可广泛用于电力系统暂态行波的测量。

1 前言

对电力系统高压输电线路进行精确的故障定位是保证系统安全稳定运行的有效途径之一。现代行波定位是通过对故障发生后线路出现的电压行波和电流行波的采样值进行综合分析,确定故障行波波头到达线路上测量点的准确时刻,来实现精确的故障定位。输电线路短路故障发生后的暂态行波信号,其不同频率分量具有不同的速度和衰减。波头的形状和极性与线路两端的波阻抗变化情况有关,幅值与故障发生的时刻密切相关,使得行波在传播过程中易发生畸变,降低了对行波准确到达时间的判别及对行波反射波的识别能力。对于变化速度极快,变化过程极短的高速瞬态行波信号的采集,需要高速A/D转换单元、大量数据存储单元、高速寻址和快速存储等。

为了用单片机实现对μs级甚至ns级高速瞬变信号进行采样,研究了一种基于GPS同步的、用硬件电路实现高速数据采集、高速寻址以及存储的技术,保证了高速瞬态信号的实时采集。从而提高了输电线路故障定位的精度。

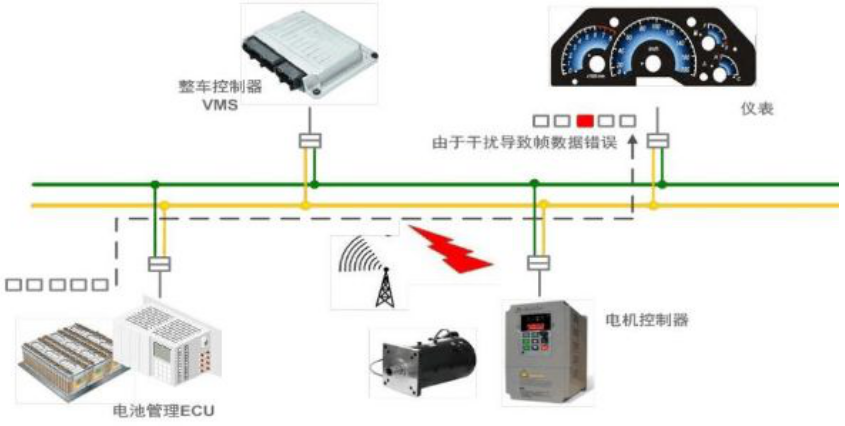

由于所采集的信号是高频信号,用常规的办法受到单片机本身运行速度的限制,使用计算机不仅造成成本提高,而且对高频、远距离多路信号的信号处理上增加困难,有时无法区别所采集信号的真伪。通过对8051单片机的外围进行有效的扩展,采取在数据采集时由硬件实现其采集和存储,采集完毕后由8051单片机进行数据处理和通信,比较好地解决了两者的矛盾。

我们研制的高速数据采集板的采样频率为20MSPS;A/D转换字长为8位,并且采样速率可变;存储容量为512K字节,符合ISA总线标准等特点。可广泛用于电力测量、继电保护和故障定位等。

2 硬件系统

对高速数据采集技术而言,最为重要的是系统的分辨率、精度与通过速率,特别是系统通过速率,是区别高速数据采集与一般数据采集最为关键的一项技术指标。在硬件的具体实现过程中,则需要考虑两个方面:(1)A/D转换器的转换时间。(2)转换后的数据存储时间[3]。

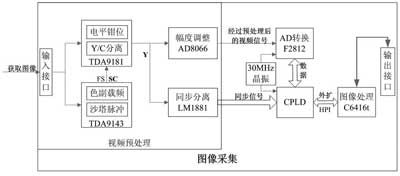

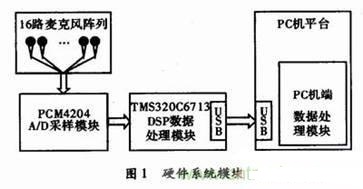

本文根据需要使用DS80C320单片机,在时钟频率为33MHz条件下,单周期指令执行时间是110ns,充分发挥高速A/D转换芯片的性能。硬件电路框图如图1所示,它是由CPU1及CPU2基本系统、视频闪烁ADC转换器、高速缓存RAM、双口RAM、地址计数器、采样频率控制、时序控制及译码电路等部分组成。

CPU1主要用于数据采集和同PC机通讯,CPU2用于接收GPS时间报文,GPS时间报文可在任何时刻由CPU1从与之相接的双口RAM2中读取。选用高速双端口RAMIDT7130(2k×8位)、IDT7134(4k×8位),内部具有判决电路以防止因对某一单元同时操作而产生冲突。第一片双口RAMIDT7134主要是用于CPU1存放采集的数据、同步时间信息及工作状态等量,供PC机定时取用,同时也接收来自PC机的命令。第二片双口RAMIDT7130其容量为2K字节,主要用于CPU1与CPU2交换GPS的同步时钟信息。

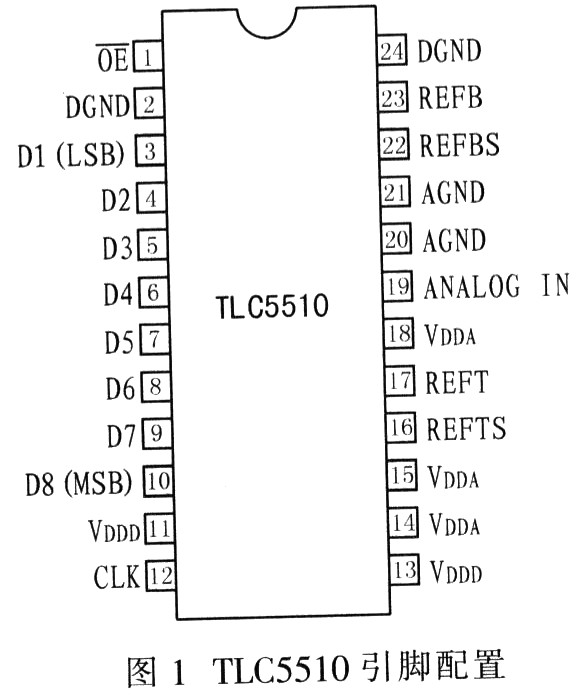

2.1 高速A/D转换

A/D转换采用闪烁ADC器件AD9048,其最大转换速率为35Ms/s,分辨率为8位。AD9048内部时钟锁定比较器,可使编码逻辑电路和输出缓冲寄存器工作在35 MSPS的高速,并避免了多数系统对取样保持电路(S/H)和跟踪保持电路(T/H)的需要。AD589和AD741,2N3906等构成稳压可调电路,提供给9048的RB,RT接地。AD9618作为输入缓冲放大器[4]。由于AD9048的数据输出没有三态门控制,故在输出加以74LS241作为三态门控制。AD9048是否工作取决于输入转换脉冲信号,在脉冲信号上升沿取样。转换脉冲来自采样频率控制电路中的8254分频器的输出。

2.2 高速寻址

对于高速数据采集系统A/D转换应不受CPU控制,每当ADC转换一次之后,由控制电路发出相应的信号,将ADC转换结果写入高速缓存RAM某单元中,再使地址计数器加1,直到地址计数器记满后产生采样结束信号,控制信号封锁RAM写信号,利用二进制地址发生器的最高位通过中断方式通知主机采样已完成。

地址形成电路可根据地址位数由若干同步记数器级联而成,5片74LS163可构成19位地址形成电路。计数器每收到一个脉冲即产生一个地址,地址的初值可通过时序控制电路清零。若采用循环地址,则在记数满后,用进位信号迫使记数器的同步预置电平发生变化,使记数器恢复初值,进入新一轮记数。

2.3 快速存储

单片机与上位PC机间的串口通讯的数据传输速率往往不能满足实时性要求,DMA通道的最大数据传输率也不超过5Mb/s[1],这显然无法满足本系统中高达20Mb/s的采样速度,为了解决高速数据采集与低速数据传输的矛盾,在单片机系统中,数据存储器选用双端口RAMIDT7134,在上位PC主机与单片机之间建立了一个4k字节大小的缓冲区,单片机只须将经过预处理的采样值通过一个端口存入缓冲区,上位PC主机通过另一端口从缓冲区取数据,这

样就解决了高速采样与低速数据传输的矛盾,可满足实时采集和控制的要求。

评论