- 在无线分布式采集系统设计中,采用了基于卷积编码、Viterbi译码的编码和互为备份的双通道传输方案,利用了FPGA内丰富的逻辑资源以及存储资源,实现了数据的远距离同步可靠传输。

- 关键字:

无线分布 Viterbi FPGA 采集系统 卷积编码

- 卷积码是广泛应用于卫星通信、无线通信等各种通信系统的信道编码方式。Viterbi算法是一种最大似然译码算法。在码的约束度较小时,它比其它概率译码算法效率更高、速度更快,译码器的硬件结构比较简单。随着可编程逻辑技术的不断发展,其高密度、低功耗、使用灵活、设计快速、成本低廉、现场可编程和反复可编程等特性,使FPGA逐步成为Viterbi译码器设计的最佳方法。项目目的是用FPGA实现一个Viterbi译码器。

一、译码器功能分析

译码器是一种具有“翻译”功能的逻辑电路,这

- 关键字:

FPGA Viterbi 译码器

- 摘要 数字通信作为一种前向纠错编码技术卷积码起着重要的作用。相应地,信息接收端对卷积码的译码实现也提出了更高的要求。文中提出的卷积码译码Matlab仿真方案,旨在用Viterbi译码实现对卷积码译码的功能。仿真结果

- 关键字:

仿真 实现 Matlab Viterbi 系统 通信

- 高清晰度数字电视(HDTV)技术是当今世界上最先进的图像压缩编码技术和数字通信技术的结合。它代表一个国的科技综合实力,蕴藏着巨大的市场潜力。数字电视地面广播编码正交频分复用(CMOFDM)传输系统以其较强的抗多

- 关键字:

Viterbi HDTV FPGA 接收机

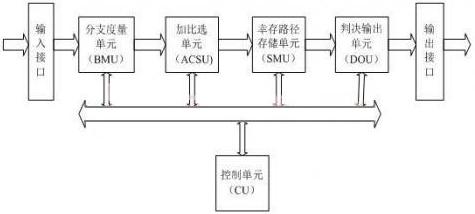

- 摘要:卷积码及其Viterbi译码是现代通信系统中常用的一种信道编码方法。文中介绍了Viterbi译码算法的原理,分析了Viterbi译码器的结构,然后用Verilog语言设计了一种基于Altera公司的EP3C120F780C8芯片的(2,l,7)Vi

- 关键字:

Viterbi FPGA 译码器

viterbi介绍

您好,目前还没有人创建词条viterbi!

欢迎您创建该词条,阐述对viterbi的理解,并与今后在此搜索viterbi的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473