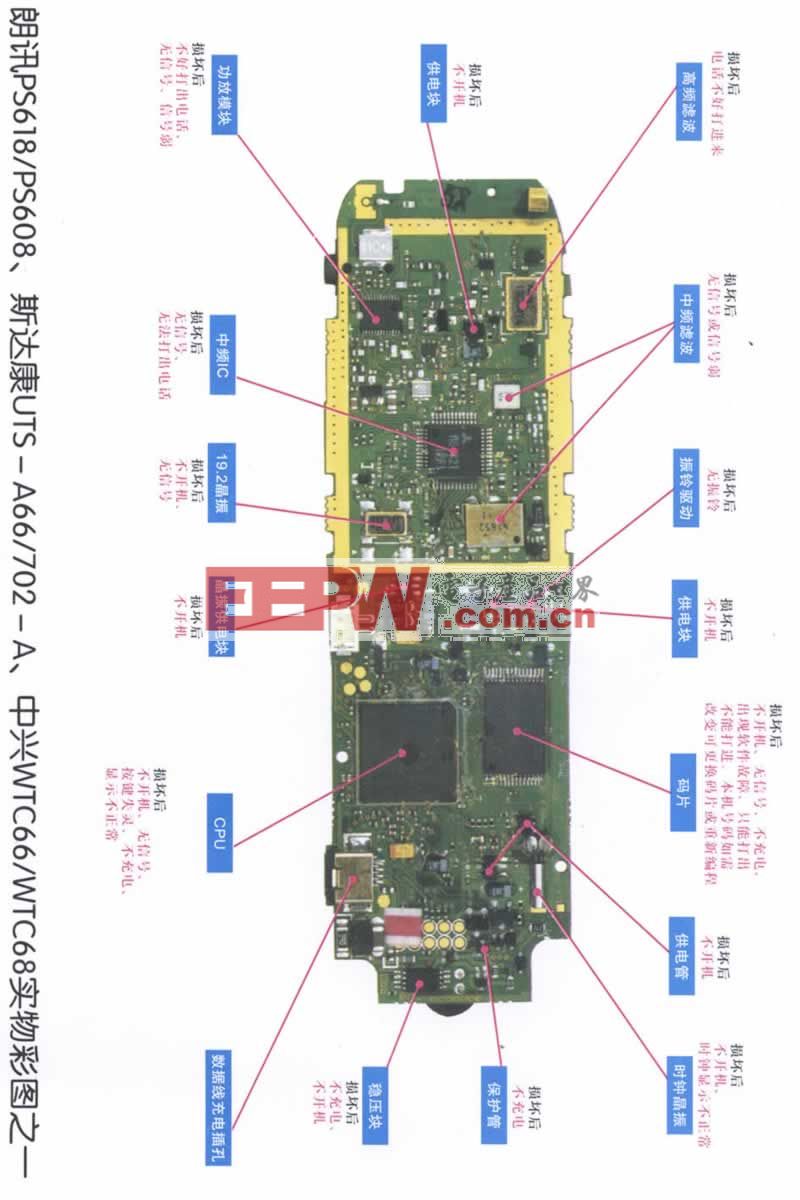

高速A/D系统设计结构及电路设计问题

在现代雷达系统、激光测距以及高能物理试验中往往产生宽带信号或者上升沿比较陡的信号(一般10ns左右)。若对此类信号进行数字化处理,要求A/D部分的采样率至少应该在200M/s以上。本文介绍的系统正是针对这样的要求而开发出来的。

本文引用地址:http://www.eepw.com.cn/article/201706/353099.htm1 系统结构

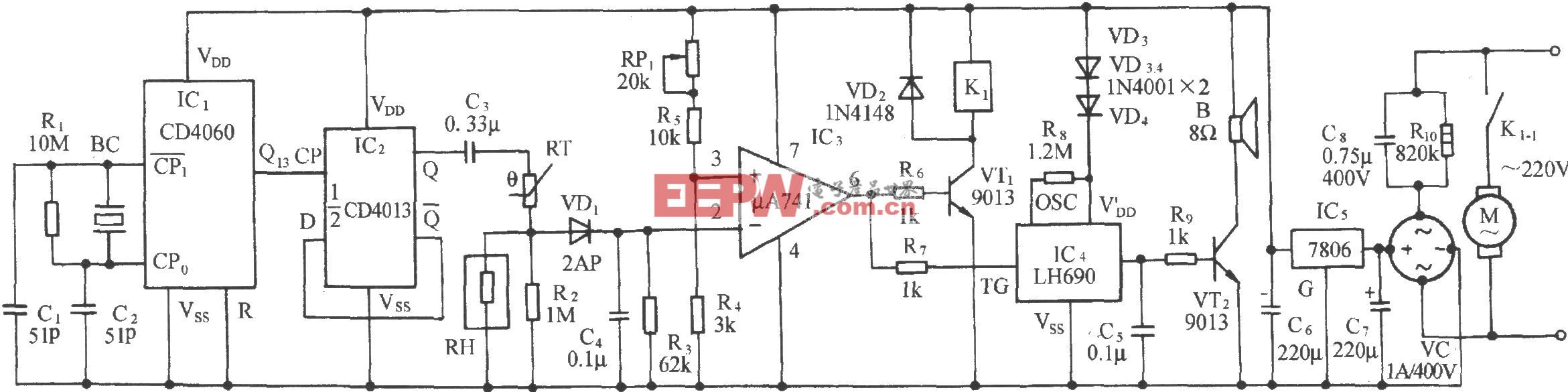

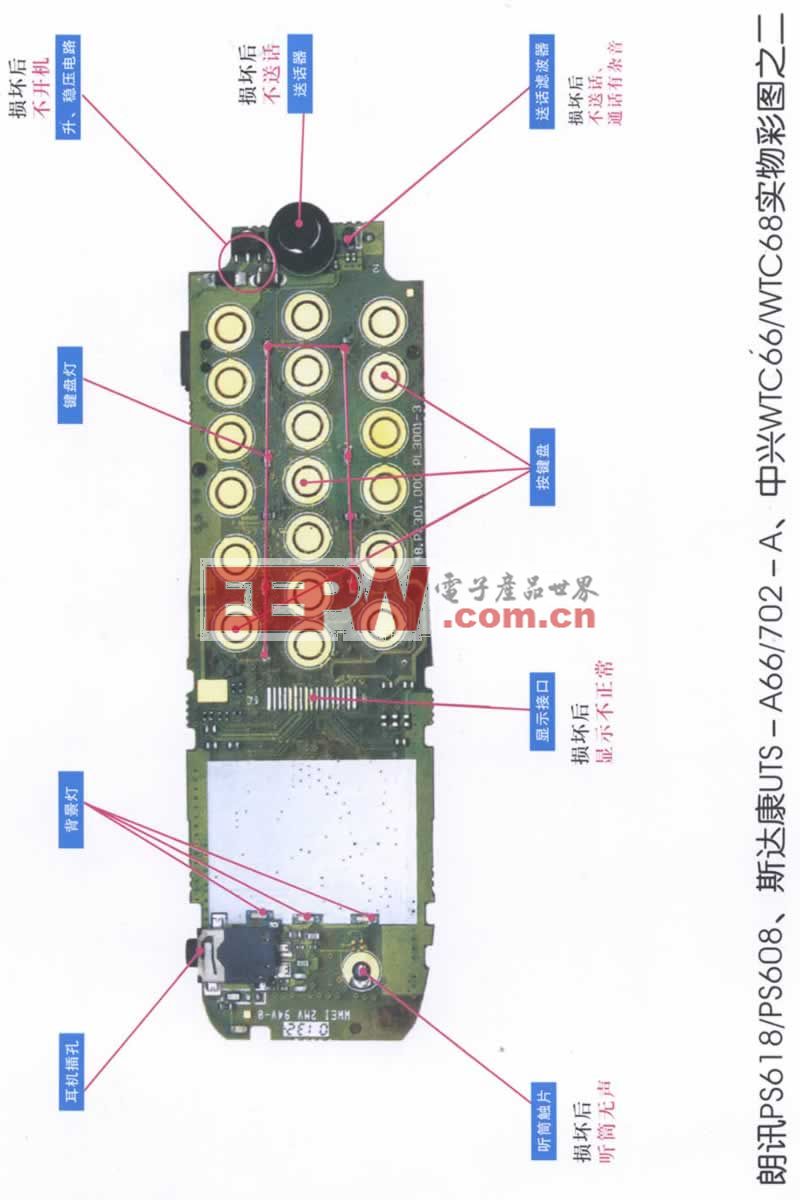

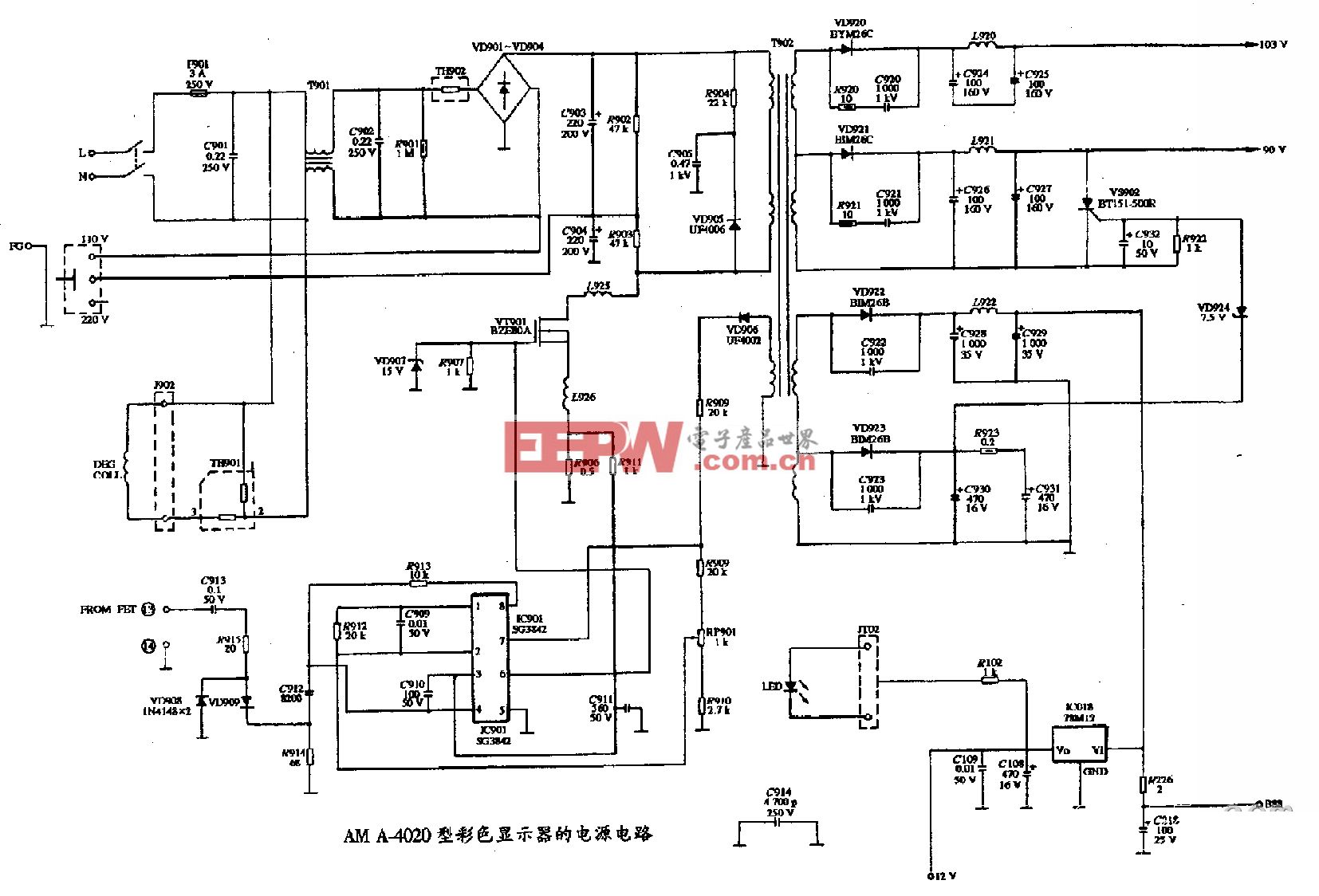

系统分为A/D转换和数据传输控制两大部分(图1)。数据传输控制部分作成PC机的插卡在计算机的PCI扩展插槽内,它的主要功能是将A/D采样得到的数据传递给计算机,同时产生相关的控制信号去控制整个系统;A/D转换部分由于受到电源和体积的影响单独作成一个模块置于计算机外部,其中关键的核心器件ADC采用的是MAXIM公司推出的MAX101A,它的最高采样率可达500兆/秒,采样精度为8bit。两部分之间的数据传递通过扁平电缆来完成。

2 A/D转换

2.1信号调理

对于高速A/D采样电路来讲,前端调理电路显得尤为重要,不仅要有足够的带宽,而且还要将单端的输入信号变成差分信号提供给ADC,以减少偶次谐波的产生,同时本身的噪声也要很小,这样才不会对ADC的精度产生影响。考虑到上述因素,在前端部分采用了AD公司的AD8138作为缓冲放大器,它的性能指标为:-3dB带宽320MHz,输入噪声5nV/(根号Hz)。AD8138为表面封装器件,本身的体积非常小巧,使得ADC与信号输入点的距离可以很近,大大减少了外界噪声的影响。经测试,器件的模拟带宽为230MHz(图2)。

2.2 系统时钟的选择

ADC芯片MAX101A要求的采样时钟为500MHz的ECL差分时钟。对于如此高速的时钟电路,孔径晃动(jitter)是选择时钟源的一个非常重要指标。Jitter是指时钟沿本身不稳定,在一定范围内晃动,时钟沿的晃动会带来采样点的不确定性,被采样信号的频率越高造成的误差就越大(图3)。经过调研,市场上有两种比较成熟的芯片可供选择。一是Motorola公司MC12439,另一个是Synergy公司的SY89424。MC12439可输出的频率是50~800MHz(Peak-to-Peak jitter 25ps 8δ),/TRK1 SY89424的最高输出频率为1GHz(Peak-to-Peak jitter 3δ)且两者的输出电平都为差分的PECL。虽然两种芯片给出的jitter相差不大,但实际上以上参数都是在输出时钟频率小于其最大输出频率一半的条件下给出的,也就是说此时的输出时钟是内部VCO的输出经过分频后得到的。如果输出时钟不经分频而直接输出,输出时钟的频率实际上是内部锁相环VCO频率的两倍,输出时钟的稳定性与VCO时钟的占空比有直接的关系。而VCO很难保证它的占空比总是50%,后以在这种情况输出时钟jitter将大大增加。鉴于上述原因,最终选择了Synergy公司的输出频率可达1GHz的SY89424。

2.3 特殊电平时钟的产生

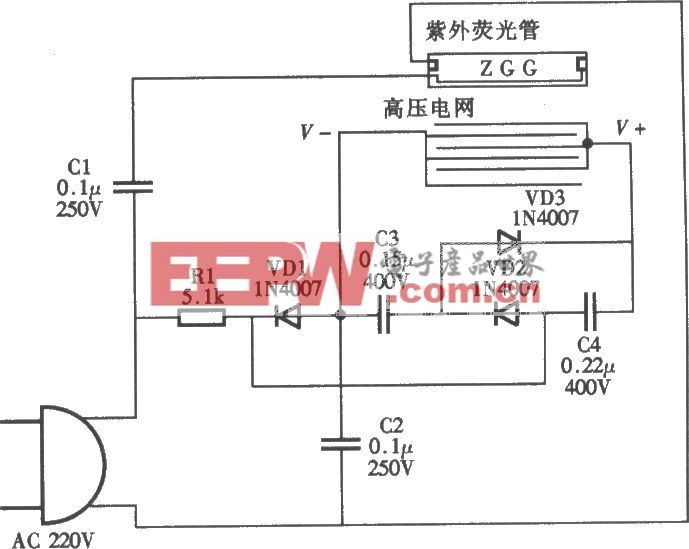

MAX101A芯片内部是由采样率为250兆/秒的完全独立的两个ADC拼在一起而得到的,从模拟信号输入、参考电压到数字信号输出都是完全分开的两部分。这样做给与用户很大的自由度,但同时也带来一个问题,那就是很难确定在每一次上电后究竟是哪一个ADC先输出,从而无法正确地进行数据锁存。MAX101A要求用户提供一个外加的控制信号TRK1和TRK1来确定两个ADC的先后顺序。它规定在系统采样时钟的下降沿到来时,如果TRK1为“1”,/TRK1为“0”则第一个ADC输出有效,反之则第二个ADC输出有效(图4)。这样的控制信号实现起来并不难,但MAX101A对TRK1和/TRK1的逻辑电平范围的规定是一个非常规的值,它规定输入电平在±50mV之间为逻辑“1”,在-350mV到-500mV之间为逻辑“0”。对于这样一种非标准的时钟电路,不可能用现成的芯片直接产生,为此在模拟伪真结果的基础上,采用了图5所示的电路来产生这样的时钟信号。D触发器将时钟信号二分频后经隔直电容送到电阻分压网络进行衰减,同时提供新的基准电平,这样原来的ECL信号(-900mV~-1800mV)就被转换成在0~-450mV之间的时钟信号,满足了MAX101A的要求。电容隔直方法在高速数字电路中应用十分广泛,应用这种方法可以很方便地将不同电平范围的信号(如ECL和PECL)进行相互转换而不需要额外的电路,使用起来相当方便。

2.4 高速数据的锁存

高速ADC的数据锁存在A/D系统里的设计一直都是一个难点,ADC的速度越高数据锁存的难度就越大。尽管MAX101A的数字输出已经分成了A、B两个端口,使每个数据通道的速率降为250Mbyte/s,但要将如此速度的数据准确无误的锁存下来还是相当困难的,必须进一步降低数据端口的输出速率。降低端口速率唯一的办法就是将输出端口的数据分成多路交替输出,使每一路的数据产生率降到可以接受的速度。但是分的路数越多,电路就越庞大,各种时钟与数据之间的关系也就越复杂。综合两者考虑,采取了将ADC的输出分成八路的方案,这样每一路的数据产生率为62.5Mbyte/s,完全可以用普通的锁存器来完成。数据锁存部分的结构如图6所示。

MAX101A输出的锁存时钟(250MHz)经四分频后送入一个六位的移位寄存器产生6个相差4ns的时钟,其中的ABCD用于锁存各个端口的数据,CDEF经电平转换后作为EPLD锁存数据的时钟,之所以推迟两个时钟是为了补偿数据的传输延时和EPLD内部FIFO的建立时间。数据进入到EPLF后,后端的处理就方便得多了,可以用EPLD作DRAM控制接口将FIFO的数据存储到大容量的DRAM中去,也可将数据分组打包通过传输介质传递给计算机进行处理。在本系统中,采取第二种方法将数据通过电缆传递给位于计算机内的一块PCI卡上,计算机再通过它把数据存放到硬盘上。

3 高速电路的设计

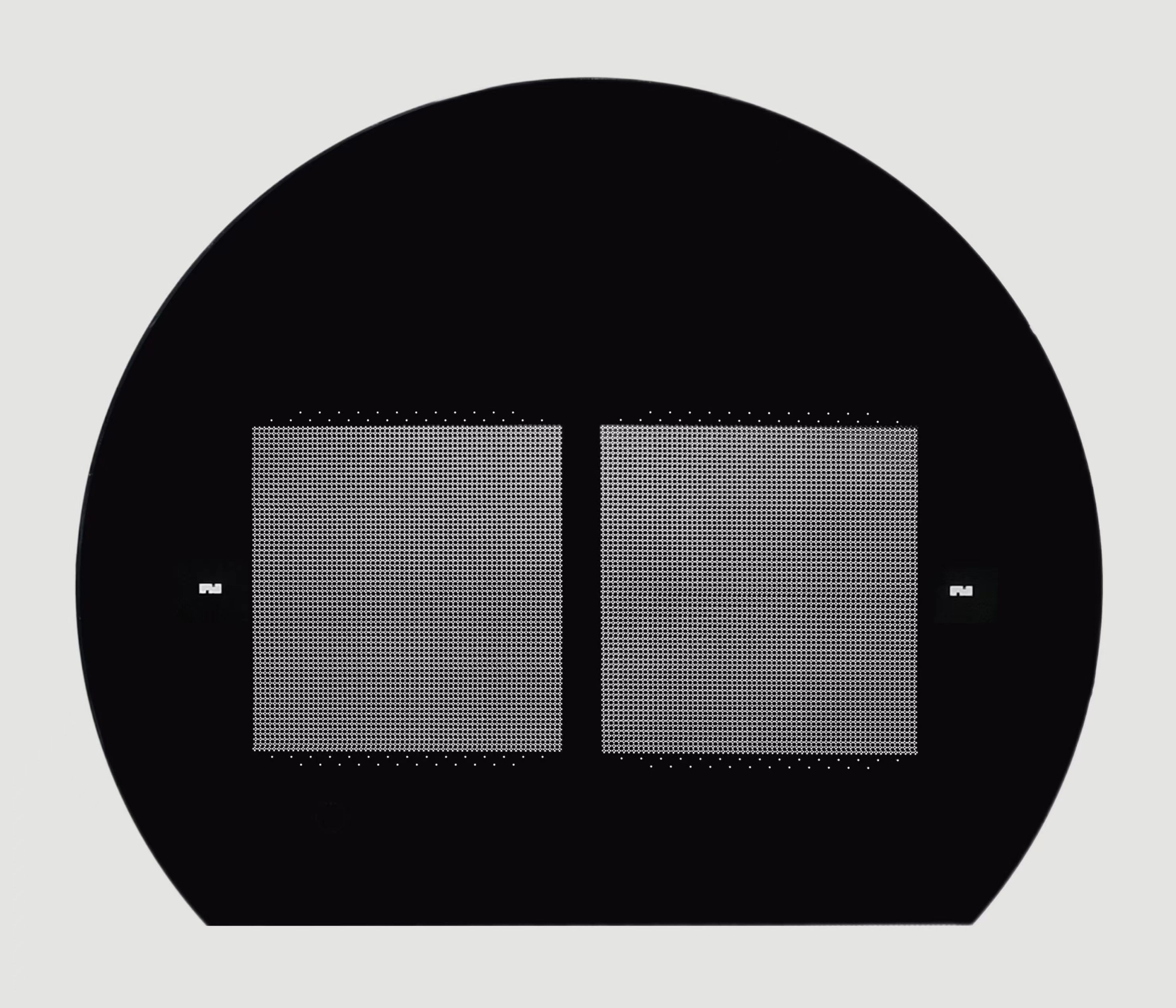

在高速电路中如何避免各个信号之间的串扰(crosstalk),以及如何保证信号的完整性(integrality)是整个系统正常工作的保障。首先,对于高速电路电路板(PCB)应至少采用四层以上的多层板技术,本系统采用了六层板(表1).采有多层板的目的并不仅仅是为了走线的方便,更重要的是使用了大面积的电源或地层之后可以使各信号线与地或电源平面之间形成一个紧耦合从减少信号线之间的串扰。通常所用的在走线层大面积网格铺地的方法,虽然也可起到一定的屏蔽作用,但其面积和与信号线距离的关系远不如地平面产生的效果好。其次,系统的整体布局要合理,应该综合考虑地平面和电源层的分割。使用相同电源和地的芯片,布局尽量放在一起以避免地平面被琐碎的分割。当同一块电路板上既有模拟电路也有数字电路时,更应该仔细地考虑这两部分的布局。模拟部分和数字部分应该隔离,不仅是空间的隔离,而且电源也应该隔离,两部分最好单独供电。最后,模拟地和数字地通过磁珠(ferrite bead)在一点相连。地平面上的电流一般比较大,大电流流过时会对表面上的器件产生一公平的影响,尤其是对模拟器件产生的影响将直接反映在输出信号质量的好坏。为了减少地电流的影响,在设计地平面时应该在比较敏感的模拟器件下方加一道隔离沟阻断大电流的通路(如图7所示),以减小地电流对它的影响。

表1

名 称 用途说明

顶层 布线、元件

中间层1 模拟地、VTT

中间层2 数字地、ECL的VCC

中间层3 模拟+5V、数字+5V、数字+3.3V

中间层4 模拟-5V、数字-5V、数字+2.5V

底层 布线

高速电路的PCB设计是整个系统成败的关键,PCB的设计在很大程序上与所选用的EDA工具有关。在本系统的PCB设计上选用的是PADS公司出品的PowerPCB,它和传统的设计工具Protel相比有如下优点:

(1)支持圆弧拐角布线,减少信号线的辐射,降低串优;

(2)支持泪滴焊盘,使走线阻抗变化均匀,减少反射;

(3)可以方便地在PCB的内部层进行分割和走线;

(4)支持多种布线规则,如布线长度、走线阻抗等规则;

(5)与自动布线器Specctra接口方便;

(6)直接支持信号完整性分析软件HyperLynx。

鉴于以上种种优越性能,它非常适合于高速电路板的PCB设计。

4 Windows95下软件设计的实时性考虑

本系统的软件运行于Window 95平台之上的。设计的指标要求每秒能计时200次的操作,每次采集512点,既要求系统在5毫秒内将A/D部分采到的512Bytes传到计算机并存储在硬盘上。这个要求对于PCI接口来说是非常低的,实测结果显示系统的平均反应时间远小于这个时间。但是结果显示系统的平均反应时间远小于这个时间。但是我们发现系统每处理10 000次响应总会有一到两次的反应时间特别慢,超过5毫秒有时甚至达到40毫秒。而我们的系统要处理的是一个连续有序的事件,要求对每一个事件都必须做反应,否则后面的事件就会被误处理。经过分析表明,这种现象完全是由于Windows95操作系统本身的原因造成的。Windows95是一种多任务的平台,它的核心运行在优先级较高的Ring0上,普通的应用程序则运行在优先级低的Ring3上,应用程序靠内核的调度分时运行。Windows95是专门为PC机设计的,主要的用途是处理人们的娱乐以及办公自动化等事务,考虑的是使用起来如何方便,并没有对工业控制方面的实时性加以考虑,所以外层的应用程序有可能会随时被内核打断,根本没有什么时间的保障。

要想准确无误地处理对时间要求比较荷刻的事件,必须把处理程序放在运行于内核级的中断服务程序中去执行,这样除非有更高级的中断否则程序就不会被打断。在编写中断服务程序处理函数时我们采用了Windriver提供的Kernal PlugIn功能,将自己编写的中断服务程序挂接在系统内核上。用此种方法可以实现每秒10 000次的断处理而不丢失。我们在编写中断服务程序时借用了硬件设计中FIFO的思想,先在内存中开辟一块共域作缓冲区分别设置读指针和写指针,硬件触发中断后服务程序先从A/D读取数据进行处理,然后发了指令控制A/D等待下一次事件,接着向上层应用软件发出消息请求上层应用程序从缓冲区读取数据存盘和显示。中断服务程序发出的消息有可能不会马上被上层应用程序响应,但只要缓冲区足够大,每一次事件产生的数据就不会丢失。整个程序的流程图如图8所示。

本数据采集系统成成功地在上海某科研单位得到应用。虽然设计初衷是为了满足某用户的需求,但它容易扩展成通用的A/D采样系统应用于相关的各个领域。

评论