基于CPLD的异步ASI/SDI信号电复接光传输设备的设计

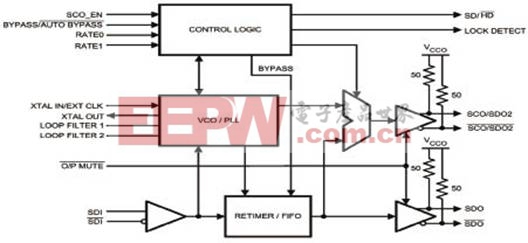

图4 时钟恢复部分电路处理过程

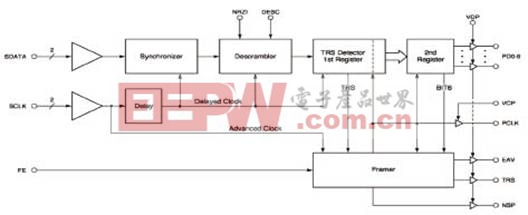

解码部分电路处理过程由图5所示。通过图5可以看到,由时钟恢复芯片恢复出来的串行时钟和串行数据输入到解码芯片,通过串/并转换后输出10位并行数据和27M的并行时钟,以备下面FIFO电路的时钟调整使用。具体各个工作模式下信号的时序图见图6。

图5 解码部分电路处理过程

图6 各模式信号时序图

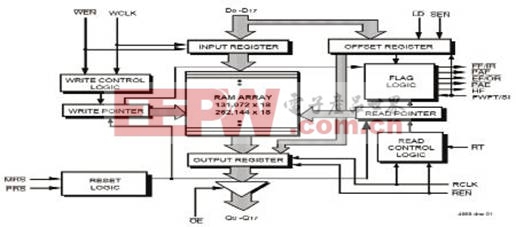

FIFO部分电路处理过程如图7所示。其中读时钟使用编码电路恢复出来的27M并行时钟,写时钟使用本地的27M时钟,通过调整实现经过FIFO的10位并行信号与本地时钟同步,为接下来输入到CPLD进行电复接做好准备。CPLD的电复接部分程序如下,其中2BP-S为复接程序,2BS-P为解复接程序。

图7 FIFO部分电路处理过程

评论