一种低压高线性CMOS模拟乘法器设计

1.2 电路实现

式(2)与式(3)中的平方运算可以由4个工作在饱和区的NMOS管实现,平方项中的减法运算可以由减法电路实现,如图3所示。本文引用地址:https://www.eepw.com.cn/article/179291.htm

将这种减法电路和4个工作在饱和区的NMOS管相结合,得到一种新型的CMOS四象限模拟乘法器,如图4所示。

如上述,定义图4中2个差分输入对分别为Via1=V1-V2;Vid2=V3-V4,输出端Vo1,Vo2。为了使电路工作在饱和区,最小的电源电压必须满足:

最终输出Vo,由式(6)、式(7)相减可得:

由输出式(11)可知,该乘法器的输出增益仅由负载电阻R,以及M9~M12晶体管的跨导参数决定。相比图1所示电路结构,节约4个电阻,减少了版图面积,电路结构更为简单。

2 电路仿真与分析

对图4所示乘法器使用HSpice仿真软件进行仿真,其中MOS晶体管模型参数由典型0.18 μm CMOS工艺提供。电源电压为1.8 V,仿真结果显示,在1.8 V的工作电压下,该乘法器静态功耗可低至80μW,其线性输入范围达到±0.3 V,-3 dB带宽可达到1 GHz。

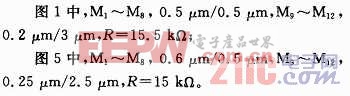

为合理比较图1和图4所示两种乘法器性能,将它们静态功耗和转换增益设为一致。晶体管参数设置如下:

其中2个电路静态电源功耗均设为195μW;图1中,Vid1,Vid2的共模电平设为0.66 V;图4中,Vid1的共模电平设为0.6 V,Vid2的共模电平设为0.2 V。

评论