基于FPGA和DDS的数控信号源的设计与实现

3 系统仿真与验证

在QuartusIl开发平台中,将在FPGA中实现的各个模块连接起来得到系统顶层模块,其仿真结果如图7所示。仿真时系统时钟频率设置为与硬件系统时钟一样fclk=50 MHz,则时钟周期为20 ns。图7是在Mode=5×107,N=32,Fword=(E883CO)H时的仿真结果,其中图7(a),图7(b)和图7(c)分别是正弦波、方波和三角波的仿真波形,从仿真图中观察它们的波形周期均为2.1μs,即换算成频率是476.190 kHz。从图7(b)和图7(c)看出,波形转换快速,只需6个时钟周期即约为12.3μs。本文引用地址:https://www.eepw.com.cn/article/177446.htm

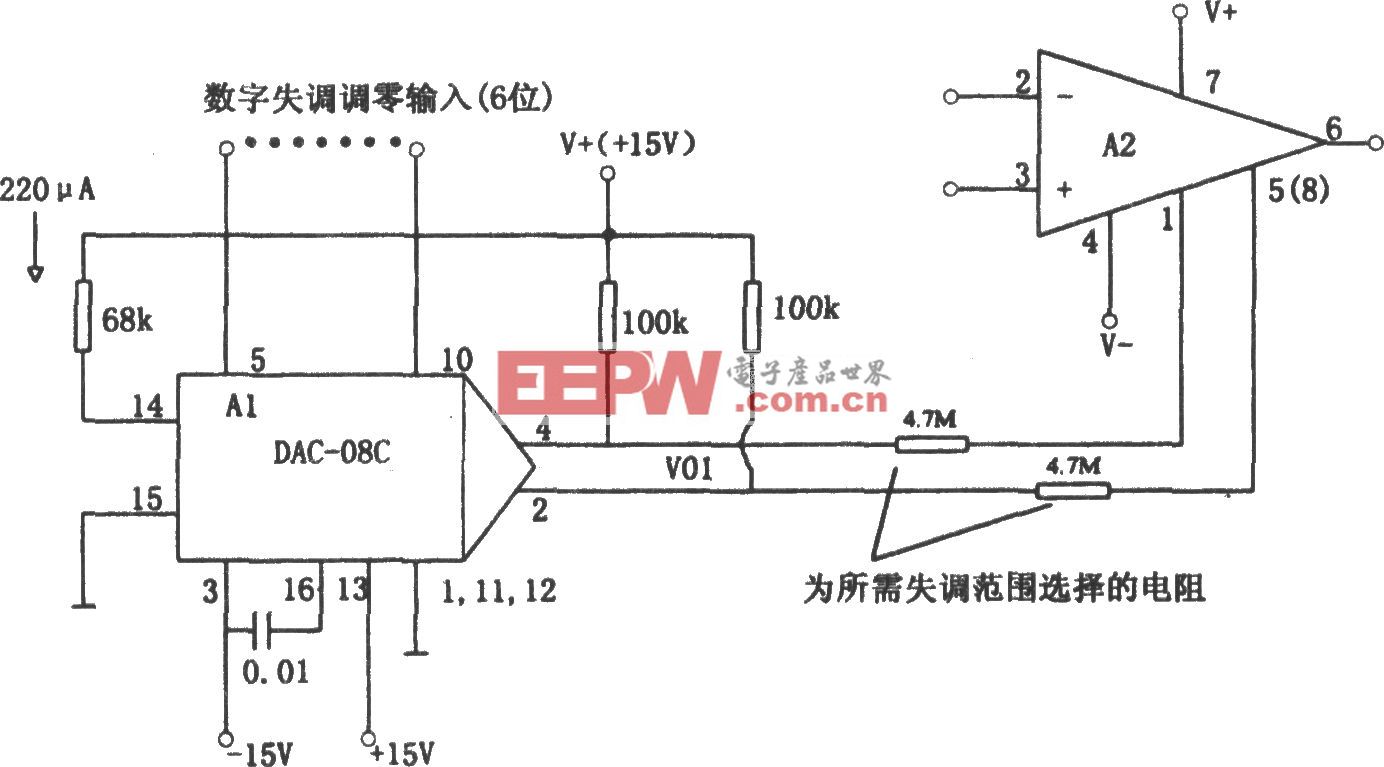

系统FPGA芯片采用EP2C8Q208,系统时钟50 MHz。D/A转换采用8位无符号DAC0832集成电路,低通滤波器采用LM324集成电路和RC网络组成的有源低通滤波器。

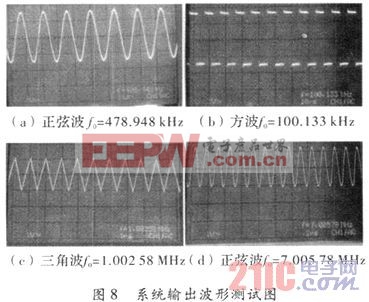

系统仿真正确后,将设计代码下载到FPGA芯片中,然后用示波器测试输出波形结果如图8所示。其中图8(a)是在频率控制字与仿真图一致时,示波器的测量结果。从图8中看出,系统能够正确输出正弦波、方波和三角波,而且输出频率为7 MHz时波形质量依然良好。

4 结束语

介绍了一种基于FPGA和DDS技术的数控信号源的设计和实现方法,并给出系统仿真和硬件测试结果。设计方案主要在FPGA芯片内实现,外围电路简单。设计的系统能够输出正弦波、方波和三角波,输出波形在整个频率范围内波形质量均好,精度达0.03Hz。

评论