CMOS器件抗静电措施的研究

高压静电场靠近CMOS器件时,例如人体带来高压静电场而用手摸装CMOS器件的塑料管虽然人体没有触及CMOS的栅极管脚,但是电场是可以穿越过去的,因为电场是绝缘不了的,它只能用金属板或金属盒子来屏蔽,所以这个高压静电场在CMOS栅极氧化层的一个面上感应带内部电场,如果这个感应电场的强度超过了CMOS栅极的击穿电压,则CMOS栅极同样会被击穿而失效的。

如果CMOS器件受到静电损伤而产生失效,那么失效有两种结果:

1)当即损坏失效:

2)延迟失效,过几个月或几年后产生失效。

如果属于当即失效,进行更换就能使整机工作正常,如果属于延迟失效,这就麻烦大了,因为不知道何时失效,会给整机留下严重的隐患,但CMOS器件90%是延迟失效,这就对整机应用的可靠性影响太大。因为延迟失效问题目前还没有办法把它筛选掉,所以只能采取各种防御措施。

2 在线路设计上采取抗静电措施

为了提高印刷版以及整机的应用可靠性,在线路设计上采取各种措施来保护CMOS器件避免受到静电损伤,这些保护措施主要放在一个系统,一台整机,或一块制板上的“接口处”,即它们的输入处和输出处,因为这里最容易受到外界静电的损伤。以下是各种方法:

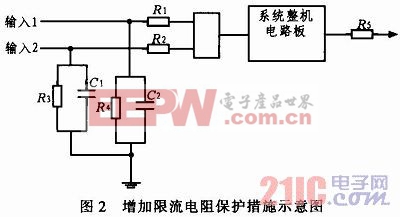

1)增加限流电阻或泄放电阻的保护措施

增加限流电阻或泄放电阻的保护措施见图2,在图2中R1,R2及R5是限流电阻,对CMOS器件选0.2~10 kΩ左右,R3及R4及并联的电容C1和C2对防静电有好处。必须说明增加泄放电阻及电容后会影响输入波形的,电容要小。本文引用地址:https://www.eepw.com.cn/article/176960.htm

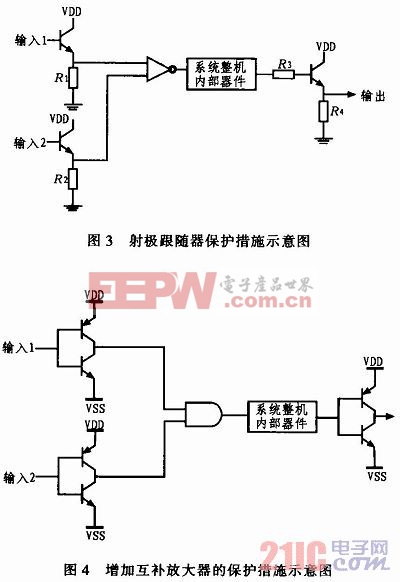

2)隔离保护措施

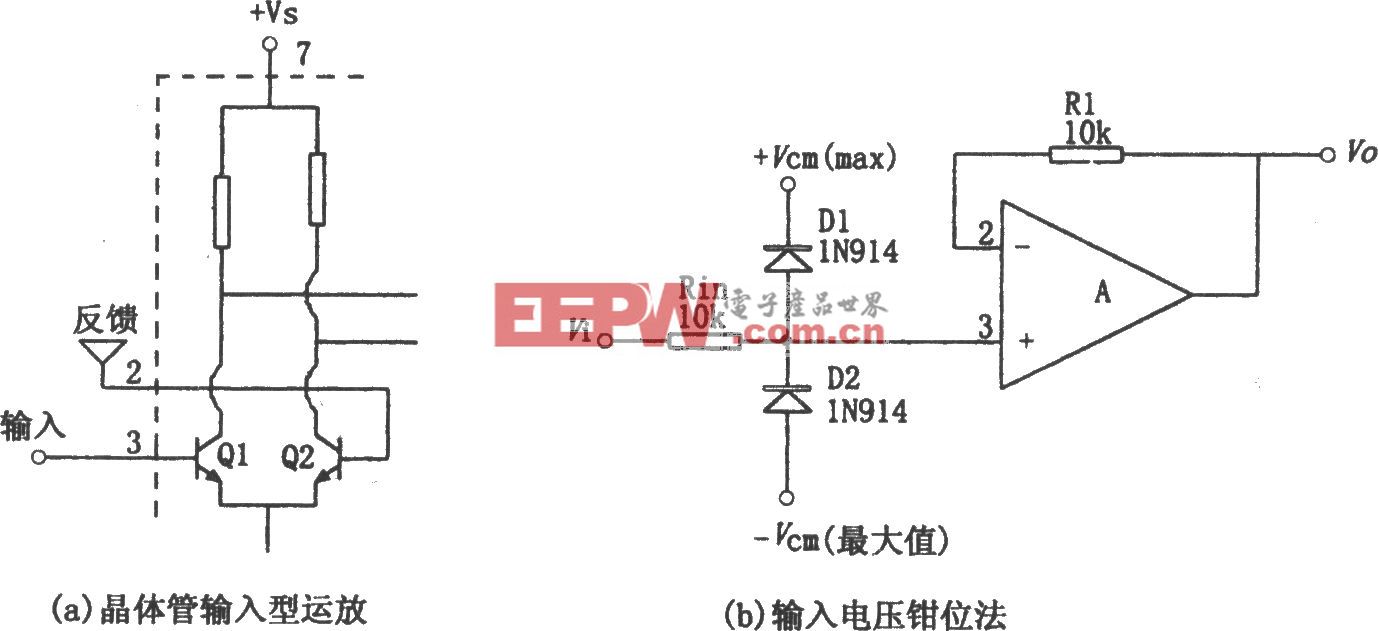

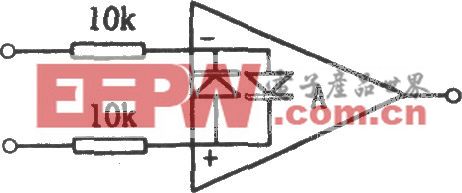

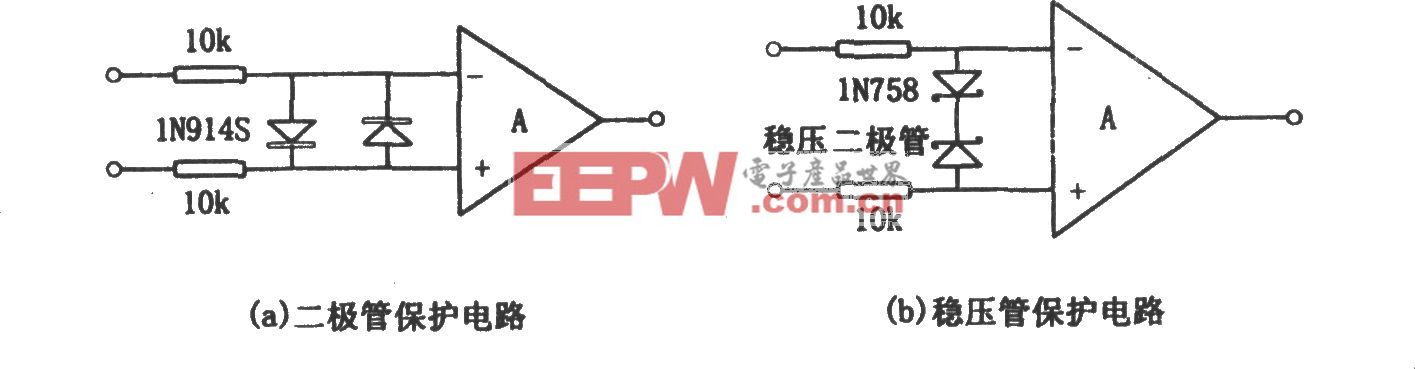

这里有几种方案,把进入CMOS输入端的静电用各种方法隔离或吸收。

①采用射极跟随器的隔离保护如图3所示。

评论