基于AD9851信号发生器的设计

2 系统硬件设计

2.1 设计方案

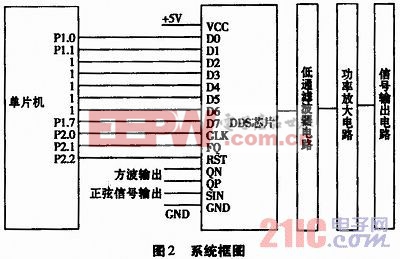

本设计方案采用AD9851芯片的并行数据模式,系统框图如图2所示。系统包含单片机电路、AD9851芯片、低通滤波器电路、功率放大电路以及信号输出电路共5部分。其中单片机电路部分选用通用的51系列单片机AT89S52,外部晶振频率为12 MHz。低通滤波器电路选用无源滤波器来进行设计,由于本设计最高输出频率为30 MHz,所以低通滤波器的截止频率在40 MHz左右。基准时钟采用贴片封装30.000 0 MHz有源晶振,为AD9851芯片提供高稳定度,高精确度的信号源。本文引用地址:https://www.eepw.com.cn/article/171641.htm

2.2 低通滤波器电路的设计

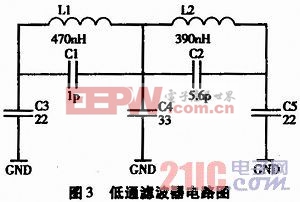

低通滤波器电路采用2阶LC椭圆低通滤波器,能有效抑制DDS的输出杂散。电路如图3所示。

2.3 功率放大电路的设计

功率放大电路采用AD828宽频带运放芯片。AD628内部集成两个运算放大器,供电方式有双电源供电和单电源供电两种,特别适合于高频信号的变换与传输。本设计中为了提高信号峰峰值的输出幅度,芯片电源采用双电源正负10 V直流电源。这样可以保证在10 MHz的带宽内得到一个相对较高的电压幅度。

3 系统软件设计

3.1 AD9851的复位工作时序

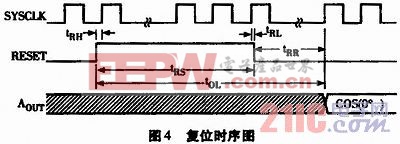

AD9851的复位时序如图4所示。从时序可以看出,AD9851芯片复位的条件是在RESET引脚出现一个高电平,并持续时间至少为trs。根据手册提供的时间参数,可知道trs最短时间是5个系统时钟,没有时间上限。由于系统电路中,单片机的晶振采用12 MHz。执行一条指令所需要的时间是1μs,为了保证复位时序的可靠性,采用复位的时间为10ms。

评论