手机功率放大器的功率包络跟踪

图6显示的是验证VSG和AWG同步和重复性所使用的设置。 NI PXIe-5673E VSG用于生成RF波形,NI PXIe-5451用于生成基带包络波形。 NI PXIe-5154 1 GHz数字化仪用于同步验证,但也可使用任何具有足够高采样率和带宽的示波器。

本文引用地址:https://www.eepw.com.cn/article/170431.htm

为了同步AWG和VSG,两个设备必须共享同一个10 MHz参考时钟。 参考时钟的来源可以是NI PXI 10 MHz背板时钟,也可以是外部提供的10 MHz时钟。

软件

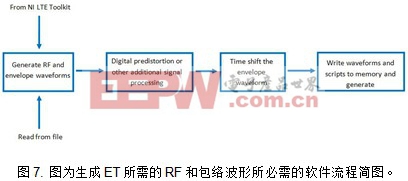

图7显示的是生成实现ET所需的RF和包络波形所必需的软件步骤。 要生成的LTE波形可使用NI LTE工具包来创建,或从文件中读取。 然后便可计算包络波形,包络波形是LTE波形的一个函数。 您也许还希望进行一些额外的信号处理,比如数字预失真或其他滤波操作来优化用于ET的波形。 可对VSG进行配置来生成LTE波形,NI PXIe-5451的配置与NI PXIe-5673E VSG中的NI PXIe-5450 AWG相似(见图5)。 接着包络波形便可相对RF波形进行时移,并与用于控制波形生成的硬件脚本一起写入到板载内存中。 (查看下面关于“波形生成延迟实现”的内容,了解包络波形时移算法。) 最后,多个设备可通过TClk来进行同步和初始化。

同步基带包络发生器和RF信号发生器所需的软件相对简单。 VSG和AWG共享同一参考时钟后,NI-TClk便可用于同步环节。 此时,对AWG和VSG生成的波形进行相位锁定,两个波形之间存在可重复延迟。 该延迟是由于NI-TClk没有计算NI PXIe-5450 AWG到NI PXIe-5611 I/Q调制器之间的模拟路径而产生的(详见图5)。 由于该延迟为常数,因此可通过设置AWG相对于VSG的延迟来进行消除。 对于许多ET应用,AWG相对于VSG的延迟(或VSG相对于AWG的延迟)对于找到延迟优化设备性能至关重要。 该延迟必须是可重复的,且具有最低程度的抖动,这是因为就算延迟只偏离最佳值几纳秒,也会使设备的线性度减少若干个dB。

波形生成延迟实现

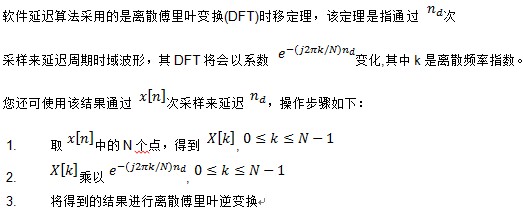

记住:VSG和AWG之间的延迟控制对于ET芯片测试和特性记述是至关重要的。 该延迟可通过在硬件中添加等待采样和偏移采样时钟或通过在软件中使用DSP来实现。 虽然在硬件中可实现该延迟,但是它需要ET波形重新采样至200 MHz才能指定纳秒级分辨率的延迟。 由于并非每个用户都能够对波形进行重新采样,因此我们更倾向于在软件中实现延迟。

电子管相关文章:电子管原理

三极管相关文章:三极管放大电路

pa相关文章:pa是什么

负离子发生器相关文章:负离子发生器原理 离子色谱仪相关文章:离子色谱仪原理

评论