基于TMS320C5402的语音信号压缩存储系统设计

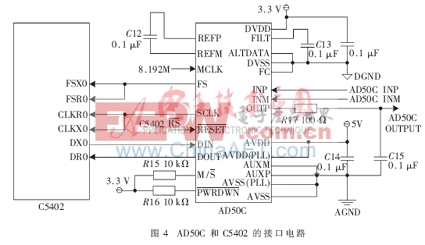

TLC320AD50C支持与TMS320C5402无缝对接,接口电路如图4所示。将TLC320AD50C设置成主动工作模式,输入主时钟MCLK为8.192 MHz,采样频率选择为8 kHz,内部PLL使能(控制寄存器4中的N=8)[2]。通过寄存器设置,将TMS320C5402的FSX、FSR、CLKR、CLKX配置为外部输人,TLC320AD50C的SCLK配置为内部产生。数据接收/发送帧同步信号、移位时钟信号均由TLC320AD50C产生,串行口的接收/发送过程受TLC320AD50C的控制。本文引用地址:https://www.eepw.com.cn/article/166635.htm

3 系统软件接口设计

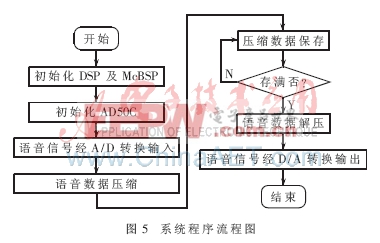

系统程序流程图如图5所示,软件设计工作主要包括以下几方面:

(1)TMS320VC5402串口的初始化。首先将DSP串口0复位,再对串口0的寄存器进行编程,使DSP串口工作在以下状态:以SPI模式运行,每帧一相,每相一个字,每字16 bit,帧同步脉冲低电平有效,并且帧同步信号和移位时钟信号由外部产生[3]。

(2)AD50C初始化。该初始化操作过程包括通过TMS320C5402的同步串口发送2串16 bit数字信息到AD50C。第一串为0000 0000 0000 0001B,最低有效位(bits0)为1,说明下一个要传输的数据字属于次通信。第二个数据用来对AD50C的4个控制寄存器的某一个进行配置。15~11位为0,10~8位为所选寄存器地址值,7~0位为所选中寄存器的编程值。通过对4个可编程控制寄存器编程,使AD50C工作在以下状态:选择INP/INM为工作模拟输入,15+1 bit ADC和15+1 bit DAC模式,不带从机,采样频率为8 kHz,模拟信号输入和输出放大增益均为0 dB[4]。4个寄存器初始化需要4个主通信和次通信。

(3)压扩算法的实现。TMS320C5402内部的缓冲串口(McBSPs)带有硬件实现的μ律和A律压缩解压,用户只需要在相应寄存器中进行设置就可以了,本系统通过软件编程来完成线性码转换成A律。在主程序中通过A/D抽样量化得到线性编码,再由编码表通过软件计算得到8 bit A律编码,其中最高位为符号位,第6 bit到第4 bit为段落码,低4 bit为段内码。将8 bit的压缩结果存储到系统RAM中进行缓存,根据抽样率、语音存储时间以及系统RAM的容量设置语音存储缓冲区的大小,待缓冲区存满后,将缓冲区内的数据进行解压缩,然后输出到SPEAKER接口输出。

4 系统实验结果

硬件调试成功后,使录音时间达到5 s左右。通过CCS观察数据图形,图6为压缩前的语音信号波形,图7为压缩后的语音信号波形;通过回放,试听解压后语音信号无明显失真。实验结果说明系统成功实现了语音信号的压缩存储。

本文所介绍的MS320C5402与TLC320AD50C的组成语音压缩存储系统,接口电路简单,编程方便,且程序代码已在CCS3.1开发环境上得到验证。

参考文献

[1] 宋依青,何松.一种基于DSP语音信号线性与非线性量化相互转换的新方法[J].微电子学与计算机,2008(11):36-39.

[2] 徐速.基于DSP的实时语音压缩[J].微计算机信息,2007(2):61-64.

[3] 李利.DSP原理及应用实用技[M].北京:中国水利水电出版社,2004:200-210.

[4] TLC320ADC/TLC320AD52C Data Manual. Texas Instruments,2002.

评论