基于NiosⅡ的学习型遥控器设计

2 硬件电路设计

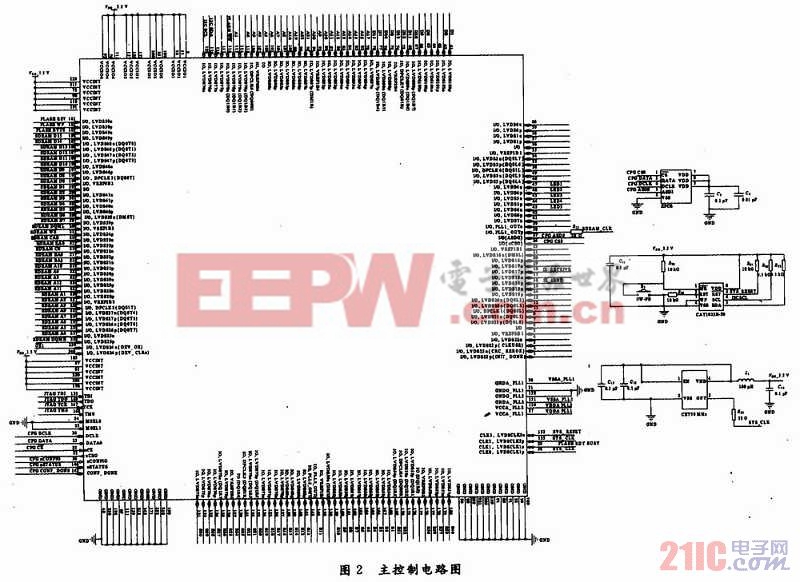

2. 1 主控制电路设计

主控制电路主要以Altera FPGA系列Cyclone EPlCl2Q240C8器件为载体,通过SoPC技术构建嵌入式软核NiosⅡ处理器平台,运用Verilog HDL硬件描述语言设计等精度测量载波频率IP核、红外信号解调IP核、红外编码脉宽测量IP核和红外发送调制逻辑电路,以实现载波的精确测量,红外信号解调、脉宽测量和调制功能。复位电路采用了专用看门狗芯片CATl025,以避免电路的死循环,同时也可以通过手动按下复位键,使系统重新启动。时钟是采用外部时钟方式,其频率为50 MHz。主控制电路图如图2所示。

2.2 外围硬件电路设计

2.2.1 按键与指示电路

为了简化软件程序,结合FPGA多I/O口的优势,本设计采用独立按键方式,当按键按下时,FPGA对应的I/O口会检测到低电平;按键弹起时,FPGA 对应的I/O口会检测到高电平。对于指示电路,采用不同颜色的发光二极管来指示不同的状态或控制不同的家用电器,当其中的一个指示灯闪烁时,表示正在学习对应的家电遥控器或者是发送对应的家电遥控信号。

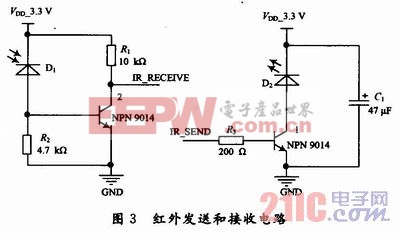

2.2.2 红外接收和发送电路

红外接收电路由红外二极管、三极管9014及电阻组成。当未检测到红外信号时,红外接收二极管电阻很大(近似于断路),三极管9014处手截止状态,此时 IR_RECEIVE端检测到高电平;当检测到红外信号时,红外接收二极管电阻较小,这时三极管9014发射极正偏,集电极反偏,三极管处于放大状态。红外信号通过共发射极电路放大后输入到FPGA的I/O口18脚,交给Nios软核进行处理。发送时,经过红外发送调制逻辑电路调制后的红外信号从FPGA I/O口16脚输出,红外信号通过三极管9014再次倒相放大后从集电极输出,驱动红外发射管辐射出红外调制信号,从而实现红外遥控信号的再生。红外发送和接收电路如图3所示。

2.2.3 存储电路

存储电路主要由AM29LV320DT(4 MB 16位并行总线)FLASH芯片和K4S641632H(64 MB 16位并行总线)SDRAM芯片组成。其中的SDRAM芯片起缓冲数据的作用,保存处理器及外部交换的数据信息,掉电或复位后数据丢失。FLASH闪速存储器,用于SoPC系统的程序存放和需要掉电保存的数据存放,但是,FLASH的读操作比SDRAM慢,写速度更加缓慢(相对于SDRAM而言)。 NiosⅡ系统启动后,在NiosⅡ的Boot程序把存放在FLA-SH中的程序复制到SDRAM后,再运行。

评论