电子产品面板控制芯片的后端设计

2.7 验证

对执行可制造设计后的版图进行连线验证和时序验证。连线验证包括:线是否连上(Verify Connectivity)、网格是否正确(Verify Geometry)、金属密度是否达到20%等等,运行后可以检查报告文件,发现金属填充后存在的线与线间距的违规,需要手工进行调整。

时序验证产生报告来检查建立时间、保持时间、最大电容和最大过渡时间是否满足要求,本设计满足要求。

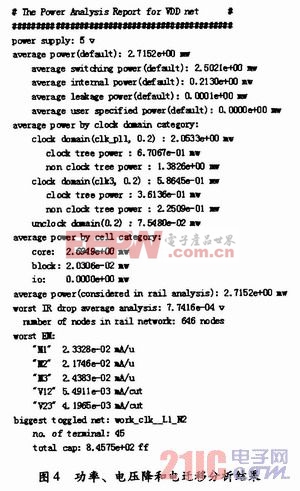

2.8 功耗、电压降和电迁移分析

对设计好的版图进行功率、电压降和电迁移分析结果如图4所示,从中可知使电源/地PAD数量、电源环、电源条的设计符合功耗、电压降、电迁移要求。本文引用地址:https://www.eepw.com.cn/article/162410.htm

2.9 输出

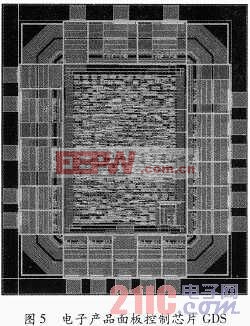

版图设计完成后,要从版图中提取进行后端验证所需的信息,如用于形式验证、物理验证、静态时序分析和后仿真的Verilog网表文件,用于物理验证工具进行。DRC,LVS和LPE的经过各单元GDS文件Merge后输出的GDS文件。将产生的GDS文件导入Virtuoso Layout Editor工具加入Cover单元并在相应的位置打上Labe1标号,最终电子产品面板控制芯片的版图,如图5所示。

3 结束语

对SoC Encounter输出的版图和网表,用Formality工具进行形式验证,用Star-RCXT工具提取寄生参数后用PrimeTime工具进行静态时序分析,用物理验证工具Calibre进行DRC和LVS,采用Modesim进行流片之前的后仿真,本设计通过上述的所有验证,成功试制小规模样片,利用搭建的测试台对样片进行验证证明达到了设计的要求。

评论