基于FPGA和USB 2.0的数字图像采集系统设计

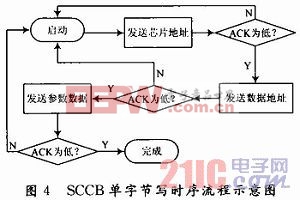

程序中使用顺序的方式,将要发送的数据逐位发送的方式来进行设置,其状态机如图4所示。本文引用地址:https://www.eepw.com.cn/article/161153.htm

将要初始化的寄存器地址以及所要设置的值直接存放于parameter定义的参数中;在上电时,通过I2C程序将这些写到OV7620当中,实现图像传感器的初始化工作。

3 CY7C68013A芯片SLAVE FIFO模式固件编写

由于系统用于图像的采集,具有数据量大,实时性要求高的特点,因此采用USB 2.0接口,以便能满足实时,高速的数据传输。为了达到最快的传输速率,使用SLAVE FIFO模式,在该模式下,USB芯片的数据传输不需要8051的参与,便于大量连续的数据传输,在这种模式下需要有一个外部的控制时序,而FPGA恰能提供相关的时序,同时为了能够与图像数据同步,采用外部输入时钟,同步传输方式,采用8位数据传输。在该应用中,寄存器EP2CFG配置了端点2作为IN端点传输FPGA来的数据至上位机,寄存器EP2FIFOCFG使能自动传输;寄存器EP6CFG配置端点6为OUT端点,寄存器EP6FIFOCFG使能自动传输;并在寄存器FIFOPINPOLAR中设置了端点的满标志为高电平有效,这是由于在刚上电下载完FPGA程序后,FPGA即对图像进行采集并存储至SRAM当中,而上电时FPGA的引脚默认为高电平,如果没有设置高电平为EP2的满有效,则在下载USB固件之前FPGA会误认为是USB的端点一直处于非满状态而一直传送数据,这样,在下载完USB固件后,主机端所得到的图像就不能保证它是从一帧图像的第一个数据开始传输而是与下一帧的图像有一定的错位。在设置EZ-USB FX2LP为SLAVE FIFO模式的过程大致是:配置IFCONFIG[1:0]=11,先把SLAVE FIFO模式;复位相应端点,即使用FIFOREST寄存器;配置所要用的端点大小,类型,以及传输方向,使用EPxCFG,式中x代表2,4,6,8;设置各端点的空标志,满标志和可编程标志值,使用PINFLAGAB和PINFLAGCD寄存器;配置是否使能自动传输以及传输的位宽,使用EPxFIFOCFG,式中x代表2,4,6,8;本应用中的USB固件程序的部分代码如下:

4 FPGA对图像数据的采集、存储及对USB的传输控制

4.1 FPGA对图像的采集控制

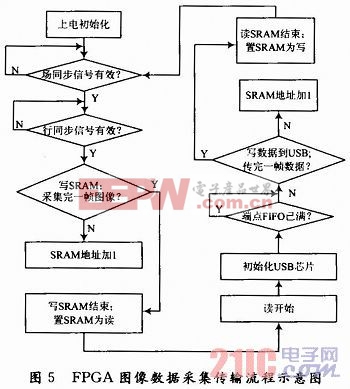

FPGA对图像的采集控制是通过OV7620的VSYNC,HREF,PCLK三个源同步时序信号来对图像进行采集。首先是在1个状态机中检测VSYNC信号,当VSYNC的高电平来临时,初始化所有的内部寄存器,包括SRAM的地址寄存器,SRAM的写控制信号,数据总线读写方向的选择信号,USB的写使能信号,内部计数寄存器等;等VSYNC来临之后,表示新的一帧开始了,接下来等待图像的行信号使能来临,当HREF到来之后,就可以将图像的数据写进SRAM当中了,这个写过程需要两个CLK,在第一个时钟周期中更改SRAM的写地址,第2个CLK周期将连接在数据总线上的图像数据写进SRAM中,同时对内部的图像计数器进行计数,这个过程中要在HREF为高电平的时候进行存储;当计数达到一帧,也就是153 600 B的时候结束采集的过程,并更改相应的控制信号,准备USB的操作信号,进行FPGA对USB芯片的控制,将SRAM当中的一幅完整的图像能过USB传至USB当中,整个采集与传送的状态流程如图5所示。

4.2 FPGA对USB芯片的控制

在FPGA完成了一幅图像的采集并将图像的数据存储在片外的SRAM当中以后,接下来要做的事情就是将所存储的图像传给USB芯片,这个过程当中,FPGA要控制SRAM的写信号,同时使能数据总线的方向为输出方向。FPGA对USB的写首先是花费一个CLK的时间从SRAM当中取出一个数据,之后在第2个CLK时间内判断它的端点满标志,如果USB端点已经满了,则等待,如果非满,则拉低写信号使能信号同时地址计数器加1,返回上一个取数据的状态继续取下一个数据,直到传完一幅图片,之后返回初始的状态重新等新的一帧开始信号的到来。

评论