FPGA设计经验谈

5)关于IP核和乒乓操作的那点事

本文引用地址:https://www.eepw.com.cn/article/158978.htm经验告诉我,能使用开发工具自带的IP核,就千万别去自己开发。往往自己开发已有的IP核是吃力不讨好。我曾经做过一个eMMC控制器烧写外部eMMC芯片的案子。

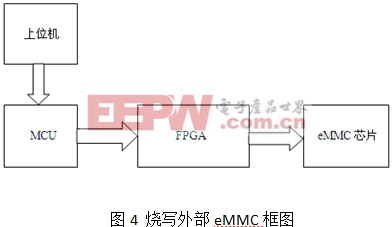

数据由上位机通过USB传给MCU,然后通过数据总线发到FPGA,在FPGA内部形成烧写eMMC芯片的时序,烧写外部芯片。框图如下:

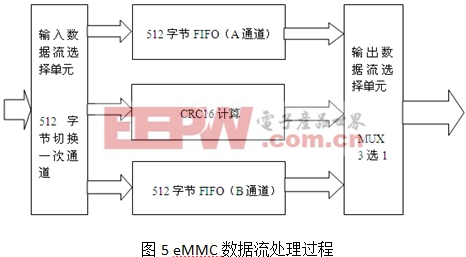

最初的算法是通过数据总线发一个字节,再向芯片打一个字节,一个页的512字节的CRC16需要事先用软件计算好,但是这种方式烧写速度太慢。后来我想到一种方案,先把512个字节传到FPGA内部存储起来,并且在FPGA内部计算好16个字节的CRC,然后用高速系统时钟一次性把整页528个字节传给芯片,这种方式烧写速度能提高很多。一开始我想自己设计一个带CRC计算的RAM或者FIFO来存储528个字节的数据,可是无论怎么设计数据传输总是有问题,由于是一个人做,也没人指导,只得放弃这种方案,改用其他。因为我用的Xilinx器件有现成的FIFO核可以调用,于是我就把CRC16的计算和存储512字节数据分开设计,在最后输出到芯片端再选通。因为烧写eMMC一个页,需要有一定的等待POLLING时间,所以我想到了用两组FIFO,乒乓操作,A通道数据发送到芯片并且等待应答的时候,MCU端向B通道发送数据存储,B通道数据发送到芯片并且等待应答的时候,MCU端再向A通道发送数据存储,这样最大化的加速了烧写速度,当然最后的设计结果我也是相当满意的。

我想通过此例告诉大家的是,尽量用系统的IP核吧,省事又省心,因为这些都是前辈专家们设计出的经典。还有就是利用一些设计技巧,比如乒乓操作,流水线操作可以让你的设计性能优化不少。

最后简单说一下体会吧,归结起来就多实践、多思考、多问。实践出真知,看100遍别人的方案不如自己去实践一下。实践的动力一方面来自兴趣,一方面来自压力,我个人觉得后者更重要。有需求会容易形成压力,也就是说最好能在实际的项目开发中锻炼,而不是为了学习而学习。在实践的过程中要多思考,多想想问题出现的原因,问题解决后要多问几个为什么,这也是经验积累的过程,如果有写项目日志的习惯更好,把问题及原因、解决的办法都写进去。最后还要多问,遇到问题思索后还得不到解决就要问了,毕竟个人的力量是有限的,问同学同事,问搜索引擎,问网友,都可以,一篇文章、朋友们的点拨都可能帮助自己快速解决问题。

逆变器相关文章:逆变器原理

fpga相关文章:fpga是什么

可控硅相关文章:可控硅工作原理

pwm相关文章:pwm是什么

c语言相关文章:c语言教程

逆变器相关文章:逆变器工作原理

比较器相关文章:比较器工作原理

评论