应用于频率合成器的宽分频比CMOS可编程分频器设计

2 电路版图设计及仿真结果

2.1 可编程分频器版图设计

整体可编程分频器的版图如图8所示,由于分频器中各单元电路都是差分结构,需要考虑到器件的匹配设计,同时对单元电路需要合理布局,以减小关键路径的连线延迟和节省版图面积。本文引用地址:https://www.eepw.com.cn/article/156400.htm

2.2 可编程分频器仿真结果

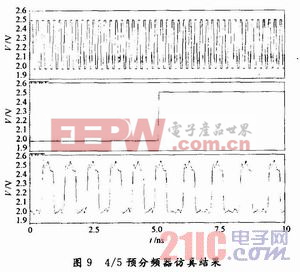

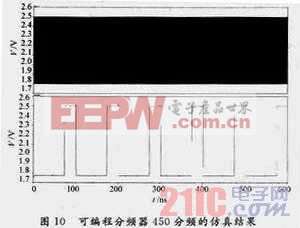

本文的仿真结果是在提取版图寄生参数后,进行后仿真得到的结果。最高工作频率可达4.5 GHz,在工作电压2.5 V下消耗功率约为19 mW。图9是工作频率在4.5 GHz下,4/5分频器的后仿真波形。图10是可编程分频器在4.5 GHz下,分频比为450,P计数器预置数112,S计数器预置数2时的工作波形。从图中可看出整个可编程分频器能够在4.5 GHz下实现正确的分频。

3 结语

对于射频频段的频率综合器,分频器成为了制约环路速度的一个瓶颈。本文通过对吞脉冲结构的可编程分频器的检测和置数逻辑电路的改进,使得分频器的工作速度可以达到4.5 GHz,满足了多标准移动数字电视接收机调谐芯片的系统设计指标,同时由于该分频器具有连续的宽分频比,使其也可应用于其他射频无线收发芯片中。同时,采用SCL结构的模拟电路实现整个可编程分频器使得芯片面积较小,约为106 μm×187μm。

评论