应用于频率合成器的宽分频比CMOS可编程分频器设计

1.3.1 传统的检测与置数逻辑设计

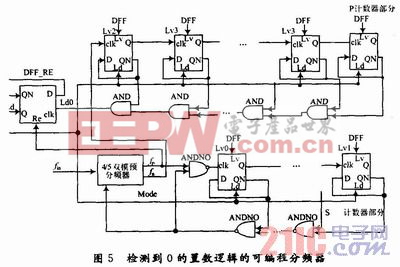

在传统的基于双模分频器的可编程分频器设计中,是对P计数器减计数到0时检测,并通过一定的时序逻辑产生一个置数使能信号使得P计数器和S计数器进行置数。其检测与置数逻辑电路如图5所示,当P计数器减计数到0时,P计数器中每个D触发器Qn端输出都为1,这时级联的与门逻辑输出从0跳变到1,形成一个上升沿(为一个检测信号)。这个上升沿作为带有复位功能的D触发器(DFF-RE)时钟输入,DFF-RE的复位端由4/5预分频器输出控制,即在严格的时序控制下,当检测到P计数器减计数到0时产生一个上升沿信号,此时DFF-RE打开,这个上升沿信号使得DFF-RE输出从0变为1,一段时间后DFF-RE关闭,故形成了一个置数脉冲,使得计数器重新置数。本文引用地址:https://www.eepw.com.cn/article/156400.htm

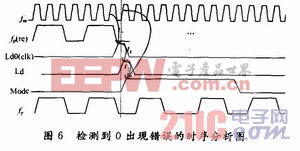

在这种结构中,检测和置数的整个过程必须在输入信号的一个周期内完成,从而限制了分频器的工作频率。下面通过对传统检测置数逻辑的时序分析来说明在输入频率较高时出现掉脉冲的现象,其时序图如图6所示,其中fin为分频器的输入信号,fp为4/5分频器的输出信号,同时作为DFF-RE的复位信号,Ld0为P计数器计数到0时的检测组合逻辑电路输出的信号,Ld为置数使能信号,即DFF-RE的输出信号,Mode为控制4/5分频器分频数的信号。由图中可知,在P计数器减计数到0时,检测逻辑输出一个脉冲(Ld0),从P计数到0到检测脉冲信号产生有一个门延迟的t0,检测脉冲到置数脉冲(Ld)的产生延迟时间为t1,Mode信号的产生延迟为t2。故从检测到Mode信号上升沿的总延迟时间为t0+t1+t2,若这个总延迟时间大于了一个输入信号的周期,如图6所示,Mode信号控制的4/5预分频器本该2次5分频变为1次5分频和1次4分

频,从而出现了掉脉冲的现象,最终导致整个分频比错误。

1.3.2 改进的检测与置数逻辑设计

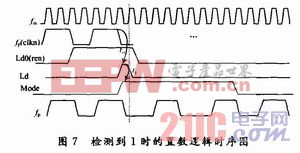

根据系统设计要求,分频器工作的最高频率需达到4.0 GHz,基于传统的检测置数逻辑的分频器很难稳定的工作在此频率下。因此,在该设计采用在P计数器减计数到1检测,通过一定的时序控制下,当P计数器计数到0时置数,这样检测和置数的过程在2个输入脉冲周期内完成,相对于计数到0检测的分频器,工作频率可以提高2倍。以下具体分析改进后的检测置数逻辑时序。在改进后的检测置数逻辑中,如图4所示,当P计数器减计数到0000001时,P计数器中DFF3~DFF7的QN端输出都为1,因此AND0输出由0变为1,AND0输出反相信号作为DFF-RE复位端信号,而4/5分频器输出的反相信号作为DFF-RE的时钟信号。其检测和置数时序逻辑图如图7所示,当检测到P计数到1后,DFF-RE便打开,置数脉冲的产生延迟为t0,Mode信号的产生延迟为t1,故由检测到Mode上升沿信号的总延迟为t1+t2,相比图6,少了一个门延迟,使得4/5预分频器正确的进行了2次5分频,避免了掉脉冲的现象。从对改进的检测置数逻辑时序分析可知,改进后的设计使得可编程分频器能够工作在更高的频率下。

评论