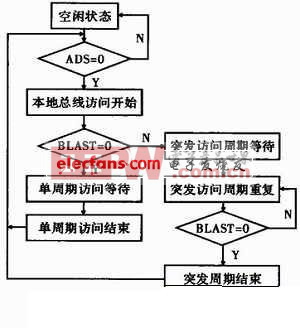

FPGA内部逻辑要设计本地端总线控制模块,实现局部总线的状态控制,同时产生片内的读写时序及地址信号以支持突发传输和单周期传输,因此使用Verilog HDL语言中的状态机来完成上述功能。其状态转换,如图4所示。

5 测试结果

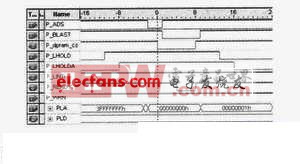

利用SingnalTap采集到的单周期时序传输图,如图5所示。

6 结束语

以PCI9054为核心介绍了CPCI板卡与嵌入式CPU板卡之间高速数据通信系统接口的软硬件设计。PCI9054因其灵活和方便的接口功能,使操作者只需关心LOCAL BUS接口电路的时序设计,并且利用其传输速率高的特性,可以帮助一些对实时性要求较高的系统解决其传输数据的问题。

评论