本文引用地址:

https://www.eepw.com.cn/article/153724.htm 2 方案设计

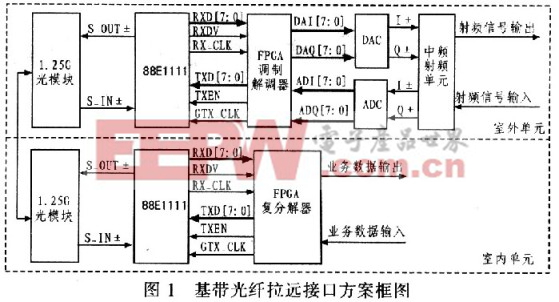

根据88E1111的功能特点和基带光纤拉远的设计要求,本文提出了用88E1111完成数字微波接力系统基带光纤拉远的接口设计方案。接口设计方案框图如图1所示,主要由室内单元、室外单元2部分组成。发方向,室内单元业务码流输入FPGA复分解器,完成业务数据打包,封装成符合IEEE802.3标准的数据帧结构,通过GMII接口发送到88E1111,由88E1111完成数据并串转换,通过高速串行信号接口将信号发送到1.25 G光收发器,完成电光转换后向室外单元发送1.25 G光信号。室外单元1.25 G光收发器接收光信号,完成光电转换,通过高速串行信号接口将高速电信号输入88E1111,由88Ellll完成数据串并转换,通过GMII接口将并行数据发送到FPGA调制解调器,完成数据解帧、调制后,通过中频射频单元向空中发送无线射频信号。收方向为发方向的逆向流程。

3 硬件设计

图2所示是1.25 G光收发器SSFF315l的电路原理图,其收发引脚RD±、TD±分别连接到88E1111的高速串行信号接口S_IN±、S_0UT±信号。图3所示是88E1111的电路原理图,其主要引脚连接关系如下:GMII接口信号(详见表1连接到FPGA;Management接口信号MDl0、MDC连接到微处理器;Config接口信号按表2映射关系连接到LED接口;XTALl引脚输入125 MHz时钟信号,频率稳定度±50 ppm;RSET为芯片参考电压输入引脚,通过5 kΩ精密电阻连接到地;SEL_FREQ为时钟输入选择引脚,接低电平时,选择125 MHz时钟输入。

88E1111完全按照IEEE802.3协议工作。TX_CLX为发送时钟,TX_EN为发送使能信号,TX_EN有效时,在发送时钟TX_CLK的上升沿传送数据,TXD[7:0]至88E1111,完成发送操作。RX_CLK为接收时钟,RX_DV是接收数据使能信号。RX_DV有效时,在接收时钟 RX_CLK的上升沿从88E1111接收数据RXD[7:0],完成接收操作。

4 设计中应注意的问题

4.1 电气接口匹配

88E111l的高速串行信号接口为CML接口,光收发器的信号接口为LVPECL接口。因此接口之间要增加CML转LVPECL电气接口匹配电路。采用交流耦合接口匹配电路时,发送端在IVPECL的2个输出信号上各加一个到地的偏置电阻,即图2中R9、R10,电阻值选取范围142~200Ω。输入端在LVPECL的2个输入信号之间跨接一个电阻,即R5,阻值取100 Ω。

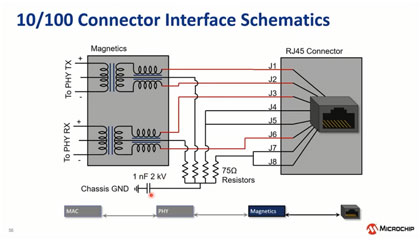

4.2 GMII接口设计

GMII接口数据速率达到125 Mb/s,速率较高,为了避免各个信号在PCB板上由于传播时延不同而造成相位误差,布线时,TXD[7:0]、CTX_CLK、TX_EN为一组信号,RXD[7:0]、RX_CLK、RX_DV为一组信号,两组信号必须严格等长。

4.3 PCB布线设计

基带光纤拉远接口板上有LVTTL、LVPECL、CML等多种信号。为避免相互干扰,PCB布线时应注意,在差分线对内,2条线之间的距离应尽可能短,以保持接收器的共模抑制能力,在PCB板上,2条差分线之间的距离应尽可能保持一致,以避免差分阻抗的不连续性。

5 结束语

基于88E1111的基带光纤拉远接口设计方案,在千兆、全双工运行模式下,接口数据传输速率可达800 Mb/s;在单模光纤传输时,传输距离可达20 km,完全达到数字微波接力系统的设计要求。本方案已在多个数字微波接力产品中得到应用,具有设计简单、性能稳定的优点。相比传统的方案有以下2个创新点:1)传输数据采用符合IEEE802.3协议的数据帧结构,接口标准、可靠;2)采用光纤作为传输介质,避免了系统的室内外单元之间馈线连接的不便,大大降低了系统成本和设备开通的难度。

评论