基于CPCI总线多DSP系统的高速主机接口设计

2.2 设计思想本文引用地址:https://www.eepw.com.cn/article/152127.htm

PCI局部端的时钟是66MHz,而DSP共享总线为100MHz,时钟的不匹配会给逻辑设计提出很多时序方面的问题。另外,PCI局部端数据总线是32位,而SDRAM数据总线是64位,如何匹配数据宽度也是一个问题。而且PCI局部端和DSP、SDRAM在控制时序上也有很大差别。

图1中显示的是共享总线结构,DSP、SDRAM和FPGA都挂在DSP的外部总线上。DSP之间的通讯可以使用DSP总线;各个DSP访问SDRAM时,也要选择DSP总线;而且当主机访问DSP通讯时,也会不可避免地使用DSP总线。因此不难得出这样的结论:DSP总线将可能成为系统的瓶颈所在。所以在设计主机接口时,必须提高总线的使用效率,减少申请DSP总线的次数,每次申请使用DSP总线时都要尽可能多地传输数据。

在微处理器设计中,Cache被用来缓存数据、解决高速CPU访问低速存储器时的瓶颈问题。为了解决上述两大问题,在FPGA的设计中也采用了类似Cache的结构来隔离不同总线间的传输。在Cache的两边有两个状态机来控制Cache的读写和总线数据的访问。使用Cache后,DSP共享总线和PCI局部端总线将被去耦合,这样可以使两级总线的数据

吞吐量都尽量达到自己的峰值速度。FPGA内部有丰富的存储资源,大块的BlockRAM可以方便地搭建成Cache;而且Cache越大,越能提高主机访问DSP和SDRAM的效率,减小占用DSP总线的时间,从而可以缩短DSP间通过DSP总线互访时的等待时间。

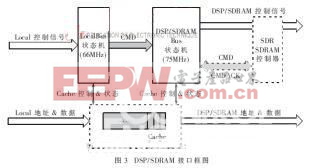

图3是DSP/SDRAM接口框图,都是基于双状态机加上Cache结构[2]。两个状态机同时监测Cache当前空、满或是数据个数等状态,以决定其动作;另外状态机间还有命令通道,局部端状态机用它向DSP/SDRAM端状态机发出命令。由于这部分跨越了两个不同频率的时钟域,因此必须加上同步电路以防止寄存器不定态的产生。

;

SDRAM接口与DSP接口不同处是它还有一个标准的SDRAM控制器,负责将自定义的SDRAM读写命令翻译成SDRAM控制信号线RAS#、CAS#和WE#的组合。将SDRAM控制器独立出来可以使得设计更加模块化,避免SDRAM端状态机过于庞大[3]。

2.3 DSP/SDRAM接口的实现

主机访问DSP时,必须遵守DSP的流水线协议,其中重要的是读写时的流水深度:读操作时流水深度始终为四个周期,写操作时流水深度始终为一个周期。主机执行来自或去往DSP的突发操作时,支持超过四字的连续突发操作。当主机发出突发首地址,只要BRST#信号有效,DSP就在内部对地址累加。首次传送的起始地址和最后一次传送的结束地址必须四字对齐。这里只支持DSP端4字突发。

评论