用FIFO实现DSP间的双向并行异步通讯

2 硬件结构与通讯流程

2.1 硬件结构

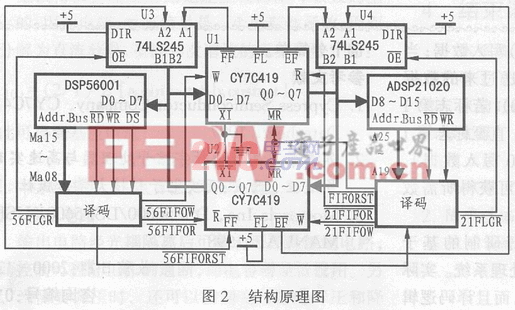

利用FIFO实现DSP间双向并行异步通讯的结构原理如图2所示。DSP56001和ADSP21020分别树熊美国Motorola和ADI公司的DSP芯片。两个CY7C419芯片U1、U2分别用于DSP56001和ADSP21020间双向并行接口的一个方向,其中U1用于完成DSP56001向ADSP21020的数据传送,U2则用于完成ADSP21020向DSP56001的数据传送。U1的全满标志(FF)与U2的全空标志(EF)通过缓冲器74LS245与DSP56001的数据总线相连,该缓冲器被映射为DSP56001数据区的一个地址单元(0x600),因此,DSP56001通过对该地址单元的读操作便可获知U1是否已写满以及U2是否有数所要读。同理,U2的全志(FF)与U1的全空标志(EF)通过一缓冲器74LS245连于ADSP21020的数据总线,该片74LS245补映射为ADSP21020数据区的一个地址单元(身份地址+0x100000),这样ADSP21020通过对该地址单元的读操作也可获知U2是否已写满以及U1是否有数据要读。另外,DSP56001对U1的写操作、对U2的读操作映射为对其数据存储区一个地址单元(0x200)的写、读操作;而ADSP21020对U2的写操作和对U1的读操作则被映射为对其数据存储区地址单元(身份地址+0x180000)的写、读操作。两个DSP芯睡均可同时对U1、U2进行复位操作。

DSP56001对双向口的读56FIFOR、写56FIFOW、复位56FIFORST及对标志口状态56FLGR的读信号可由DSP56001的地址线与读写信号译码获得;ADSP21020对双向口的读21FIFOR、写21FIFOW、复位56FIFORST及对标志口状态56FLGR的读信号则可由ADSP21020的地址线与读写信号译码获得。各译码输出的逻辑表达式如下:

56FIFOR=AdEn+Ma10+Ma9+MRD

(映射地址为:0x200)

56FIFOW=AdEn+Ma10+Ma9+MWR

(映射地址为:0x200)

56FIFOORST=AdEn+Ma10+Ma9+MWR

(映射地址为:0x400)

56FLGR=AdEn+Ma10+Ma9+MRD

(映射地址为:0x600)

评论