基于DSP 的电压闪变监测系统设计与实现

2 间接解调法误差分析及修正

对采样后计算得到的电压均方根值序列Ui(n)进行频谱分析时,由于FFT 存在频谱泄露和栅栏效应,从而导致频谱分析得到的闪变信号幅值产生较大的误差,影响Pst的计算精度。调幅系数ΔUn = 10%,不同频率fn的闪变信号经过FFT 运算后得到的计算值如表1 所示。可以看出,不同频率的闪变信号经过FFT 运算后幅值都产生衰减,而且随着频率的增加衰减更加严重。

表1 调幅系数ΔUn = 10% 对应的计算值.

调幅系数ΔUn = 10% 对应的计算值

为了补偿FFT 计算结果造成的幅值衰减,根据间接解调法提出衰减因子定义如下:

为了得到各个频率的衰减因子,重复计算30 个波形,每次仅计算一个频率成分,分别为: fn = 1,2,…,30 Hz,ΔUn = 10%;为了补偿FFT 运算造成的幅值衰减,定义修正因子如下:

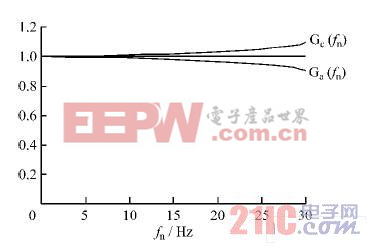

经过计算后,衰减因子和修正因子的曲线图如图1 所示。

衰减因子和修正因子曲线图

图1 衰减因子和修正因子曲线图

修正后的几个不同频率的调幅系数如表2 所示。可以看出,修正后的调幅系数非常接近给定值,大大减少电压闪变幅值的衰减。

表2 调幅系数ΔUn = 10%对应的计算值和修正值

调幅系数ΔUn = 10%对应的计算值和修正值

3 系统架构设计

3. 1 硬件架构设计

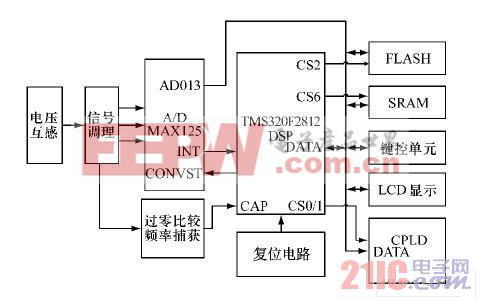

系统硬件设计是以TMS320F2812数字信号处理器为核心加上14 位双极性高分辨率的A/D转换器(MAX125) 和CPLD(EPM7128) 作为协处理器的基本架构组成。具体的硬件原理框架如图2 所示。

经过信号放大、抗混叠滤波的电压信号输入到MAX125 进行模数转换,根据采样保持定理采样频率必须大于等于2 倍的信号频率才能保证信号处理的完整性,因此,在A/D 转换前要设置信号的采样频率。调理后的信号过零比较后,送DSP 进行频率捕捉,将捕捉到的频率用于初始化DSP 内部定时器。当定时时间到来时,进入定时器中断子程序并打开A/D 采样,转换完成后MAX125 会产生一个硬件中断告诉DSP 读取数据。CPLD 作为协处理器,主要完成系统的组合逻辑、外设地址译码、数据输入输出缓冲锁存、TTL /CMOS 电平信号兼容匹配等工作。

系统硬件架构框图

图2 系统硬件架构框图.

该系统每半个工频采样128 点,然后送均方根模块进行计算,得到一个电压均方根值,在将所得的值暂存内部SRAM,连续采样2. 56 s,得到一组256 Byte 的电压均方根值,送到FFT 计算模块进行FFT 变换,对变换后的结果进行修正,将修正后的结果保存在外部的Flash 中。

连续变换一段时间后( 如10 min),根据式(4)计算出电压均方根值序列划分Ui(n) 对应的瞬时闪变值Pi,然后再根据式(5) ~ (7)依次计算短时间闪变值Pst和长时间闪变值Ph。

评论