基于FPGA的LTE系统中转换预编码的设计

2 总体结构设计

从表1中看出,LTE上行转换预编码要进行的FFT变换种类多,但每一种变换的架构是相似的,都是由基2及非基2点FFT的公共模块组成。基2有点数为4,8,16,32,64,128,256的模块,非基2的有点数为3,9,15,27,45,75,81,135,225和243的模块,只要抽出这些公共模块并精心设计,再合理地调用,就会顺利完成这个看似繁琐的工作。

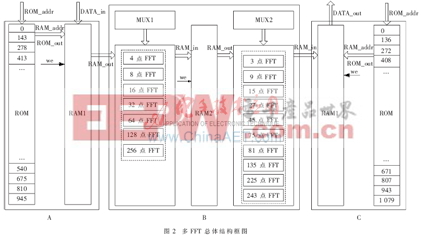

图2所示总体结构框图中,模块A和C分别为数据输入和输出模块;模块B为数据处理模块,其主要思想是动态配置和公共模块的复用,内部FFT模块事先单独生成,MUX1,MUX2是选择器,在不同输入点数的情况下动态配置不同的内部FFT模块来组合成外层FFT,这样内部FFT模块就可以达到复用的目的,可以大大减少总体资源耗用,而处理速度也与单独执行各FFT相当。

3 硬件实现

在实际应用中,一般由FPGA完成需要快速和较为固定的运算,由DSP完成灵活多变和运算量较大的任务[7]。Xilinx Virtex-5 SXT平台针对具有低功耗串行连接功能的DSP和存储器密集型应用进行了优化,具有硬件结构可重构的特点,适合算法结构固定、运算量大的前端数字信号处理,可以大量卸载这些功能,释放DSP带宽以处理其他功能,所有这一切都使得FPGA在数字信号处理领域显示出自己特有的优势。

3.1 地址映射

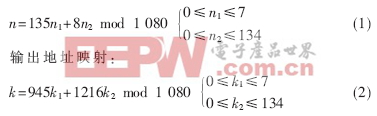

以1 080点FFT在图2所示系统中的实现过程分析系统工作原理。因为1 080=8×135,且8和135互质,故外层采用Good-Thomas算法。

输入地址映射:

FPGA内嵌Block RAM的使用可以大大节省FPGA的可配置逻辑功能块(CLB)资源。Good-Thomas算法需要对输入输出数据进行排序,输入输出端处理方法相同,这里只介绍输入端处理。在输入端,鉴于Block RAM的特征,设置一个ROM和RAM,如图2模块A所示。对于不同长度的FFT,ROM不同,但RAM可以共用。在ROM里预先存放输入数据在RAM1中的位置序号,此位置序号由(1)式得到,在时钟沿到来时,先顺序读出存储在ROM中的位置序号,将此数作为RAM1的地址输入,就能将输入数据存放到RAM1中的不同位置。这样在输入数据的同时完成了数据的排序,一举两得。1 080点FFT的输入和输出端地址索引如图2所示,其逻辑时序图见图3。图3中,RAM_in由测试数据xn_i和xn_r进行位拼接后输入。

评论