基于SOPC的车辆息线控制器设计方案

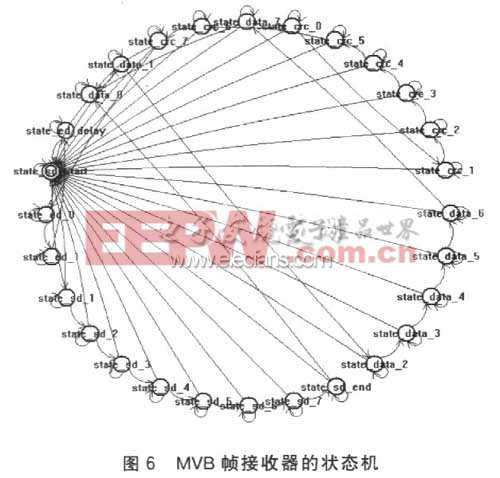

接收器实现的关键是有效数据帧的识别,实现思路类似于发送器,根据编码校验可以实现。另一个问题是与总线的接口方式,本设计采用了8位并行数据宽度输出,加序号标识的方法可以接收任意给定长度的有效数据。接收器的状态机如图6所示。

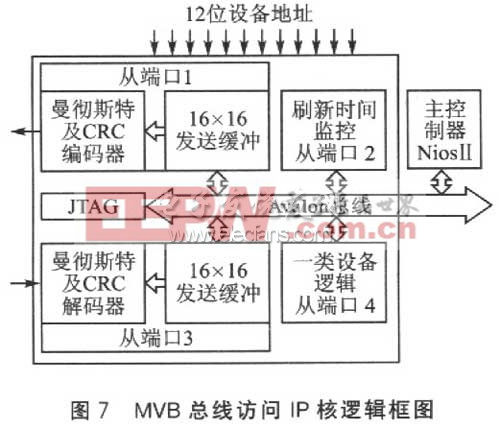

2.4 Avalon总线接口

采用Altera公司开发的Avalon交互式片上系统总线作为本总线访问IP核的内联总线,连接IP核内各个模块。如图7所示,总线访问IP核结构包括:编码器模块、解码器模块、宿端口刷新时间监控模块、一类设备逻辑控制模块。总线访问IP核内共有4个Avalon从端口,其中NiosII主控制器上设置了一个Avalon总线主端口,其他各个模块上面均设置了Avalon总线从端口,由主控制器控制总线上的数据流传输实现各个模块的协同工作,其逻辑框图如图7所示。

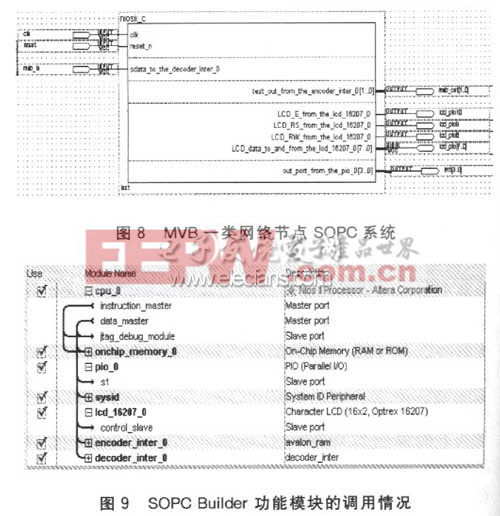

3.1 总线访问IP核与NiosII的系统集成

利用QuartersII的SOPC Builder工具,集成了1个32位NiosII软核处理器、4 KB的片内RAM、MVB总线访问IP核(包括编码器和解码器)以及LCD控制模块,在Altera的CycloneII FPGA上构成了一个能实现MVB一类网络节点功能的片上系统,如图8所示。图9为SOPCBuilder中各个功能模块的凋用情况。

评论