基于FPGA的嵌入式PLC微处理器设计

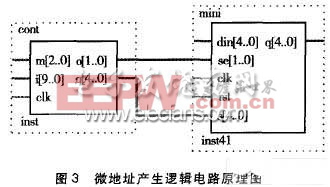

(3)微地址产生逻辑。微地址产生逻辑主要是根据微指令中的测试位及其他相关的条件来控制微地址的产生,它是根据一定的逻辑功能用VHDL语言编写的,并且经过编译和综合后生成的模块,如图3所示。

其中,clk为同步时钟信号,rst为复位信号,q为输出的5位微地址值。其控制流程如下:

(1)系统启动时,给出一个rst=1的复位信号,q端便输出“00010”,为输入扫描微程序的入口地址;(2)对应的微指令就从控存中输出,然后该微指令中的5位下地址字段直接输入到din端,3位测试位输入到m端;(3)如果m=“000”,则q端输出的地址值直接加1,且返回(2)继续执行;否则,执行下一步;(4)如果m=“001”,则看i端输入的用户程序指令来判断是否需要取数操作,如果需要,则q端输出各个取数微程序的入口地址;如果不需要,则q端根据i的操作码输出相应指令的微程序入口地址,且返回(2)继续执行;否则,执行下一步;(5)如果m=“010”,q端直接输出din的地址值,且返回(2)继续执行;否则,执行下一步;(6)如果m=“011”,则q端根据i的操作码输出相应指令的微程序人口地址,且返回(2)继续执行。

2.2 运算器

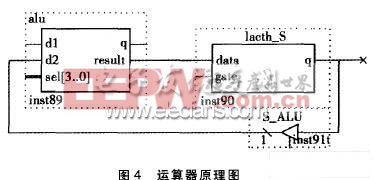

运算器是用来对输入的数据进行算术和逻辑运算的部件 ,该ALU具有三输入和两输出,d1和d2是参与逻辑运算的两个位数据,其中dl来自外部的取数,d2来自输出暂存器s,sel是指令的操作码。result是运算后的结果,输出后送给了暂存器S,q用来启动定时器,如图4所示。

2 3 RAM 图4 运算器原理图

RAM用来存储用户程序,它可以用FPGA中的LPM—RAM—DQ模块来实现。其中,wren是读写控制端,当wren=0时为读允许,这时在同步时钟clock的上升到来时沿将address所对应的地址中的内容给输出端q;当wren=1时为写允许,这时在同步时钟clock的上升沿到来时将data端的数据写入到address所指明的地址中,如图5所示。

评论