采用Max+PlusⅡ平台的CMI编码器的设计方案

其中:m_test:产生的m序列;

本文引用地址:https://www.eepw.com.cn/article/149097.htmMUX_DT:CMI编码输出;

MUX_CLK:原始时钟。

3 仿真结果

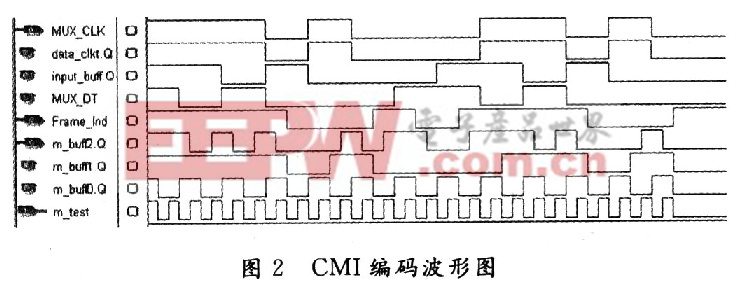

在Max+PlusⅡ平台下对CMI编码进行编译和仿真,最后得到CMI编码仿真结果。图2是CMI码编码波形图。

在时钟MUX_CLK驱动下工作,m_test是产生的m序列1011100,MUX_的DT为CMI编码输出,可以看到,编码为11010011000101,有一定延时,但编码完全正确。

4 结语

该设计详细介绍了基于CPLD的CMI编码的实现方法。提出利用原始信号的二分频后的信号求非赋值给编码输出,得到“0”的编码,利用缓存对“1”的个数进行记录,而对“1”进行编码的编程思路,利用VHDL进行程序设计实现,在Max+PlusⅡ平台下对设计结果进行仿真,结果完全正确。

实践表明,运用CPLD实现CMI编码具有软件开发周期短、成本低、执行速度高、实时性强、升级方便等特点,而且可以把该电路和其他功能电路集成在同一块CPLD/FPGA中,减少了外接元件的数目,提高了集成度,而且有很大的编程灵活性,很强的移植性,因此有很好的应用前景。

评论