通过增益校准提高DAC积分非线性(INL)

在正常操作期间,如果传到DAC的数字代码小于中间点,转换前使用第一个增益校准值来修正。如果传到DAC的数字代码大于中间点,转换前使用第二个增益校准值来修正。通过更新图3所示的gain trim registers(增益调整寄存器)校准即时完成。使用SoC里面的直接存储器存取(DMA)模块,寄存器更新速度会更快。

本文引用地址:https://www.eepw.com.cn/article/135954.htm在全范围中间改变增益修正值会产生调整偏移(见方程3)。这个调整偏移需要在算法的后半部分来补偿 (见图5)。

![]()

结果

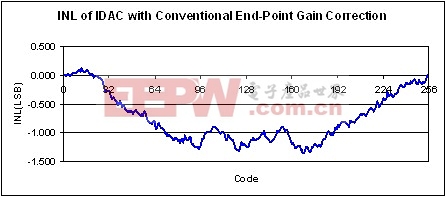

我们来做个比较,使用传统终端校验的8位电流DAC(iDAC)没有实施我们所讲的算法之前测量的INL性能,INL大约为1.5 LSB,如图6所示。

图6:使用传统终端增益校验IDAC的INL

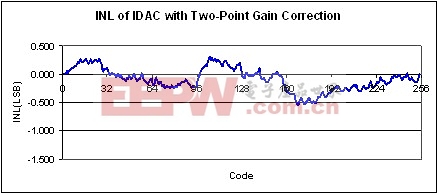

使用该算法后,INL现在降到0.8LSB,如图7所示。

图7:使用两点增益校准IDAC的INL

结论

我们介绍了SoC中用于提高DAC积分非线性 (INL)的固件技术。并以PSoC® 3为例进行了验证。对于PSoC® 3中的电流和电压DAC,该方法可以使INL改善85%。

评论