数字低通:名称虽然不同 却仍是一种滤波器

T:你让我回想起了我的逻辑课!第一个集合门的一个半加器,其中两个是全加器,其中的许多可以用二进制形式把两个数字加在一起。好了,但它看起来像一堆废物。在模拟条件下,我可以用三个电阻和一个运算放大器实现它。

本文引用地址:https://www.eepw.com.cn/article/124375.htmD:这可能有几倍那么大!图4中的集合门是几百个晶体管。利用现代CMOS工艺,在图4电路的键合点(bonding pad)你可以放进数十个这样的东西。你的运算放大器可能是这个大小的几倍。

T:好了,但它可以做什么?它是如何工作的?

D:要弄清楚它可以做什么,我们可以施加一个离散脉冲,该脉冲在0点时为1,而在其他各处为0。因此,第一个输入为1,第一输出也为1,如图3中的脉冲响应曲线所示。

T:好了,这就是你把它放在那里的原因!到目前为止很容易……

D:在接下来的时钟周期,输入下降到零(因为它是一个脉冲),而唯一的条件是通过增益块“a”来反馈,“a”通常小于1。

T:所以接下来的输出是“a”,然后下一个输出是“a*a”,再下一个是“a*a*a”……由于“a”小于1,它们在不断变小。这看起来就像在kth 样本的输出只是ak !?

D:没错。它呈指数下降,就像模拟RC滤波器的脉冲响应。

T:所以它必须有与数字信号类似的效果,即RC已经有了模拟信号。

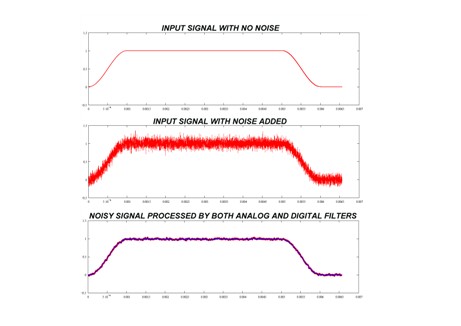

D:的确如此!下图是一个简单的脉冲信号及增加的噪声(图5)。第三张图显示了处理噪声信号的数字和模拟滤波器的输出覆盖。模拟处理的信号是红色,数字处理的信号是蓝色,但这并不重要,因为它们基本上是相同的。

图5:模拟和数字域的低通信号

(图字:无噪声的输入信号;加入了噪声的输入信号;模拟和数字滤波器处理的有噪声的信号)

T:它们是完全一样的……

D:有很多小的功能模块,这样就使数字信号处理像模拟一样简单。

T:但我仍然需要了解z-1 块。图3中的波特图似乎再次向上摆回了。为什么?怎样实现一个数字增益块?我不能只让“位”更大或更小。

D:不,不能,但我们现在没有时间。下一次我会告诉你怎样使之成为一个真正的数字电路,然后,如果你运气好,将会谈谈一个数字设计师如何把它变成Verilog代码。

T:我不明白。首先,你要继续研究时域,而不是频域,现在它是数字,而不是模拟。我对此不能肯定。

D:不,不是“而不是”,我们的想法是一起使用“时间和频率”,以得到一个更好的信号及其处理的图像。而且,我们一起使用模拟与数字,尽可能做到最好、最有效的信号处理。这是“都有”,而不是“非此即彼”。时域图像可以补充频域图像。数字信号处理的各种技巧可以补充模拟方法。我认为,未来的工程师不应该只针对模拟或数字,或者频域或时域,他们应该精通信号处理器:灵活、有创意、非常强大的信号处理器。

T:好的,不过,我想现在到了午餐的时间。

D:我们今天去Tex-Mex?

评论