一种多体制通信时间同步算法及其FPGA实现

—— Timing Synchronization Algorithm for Multimode Communication and Implementation in FPGA

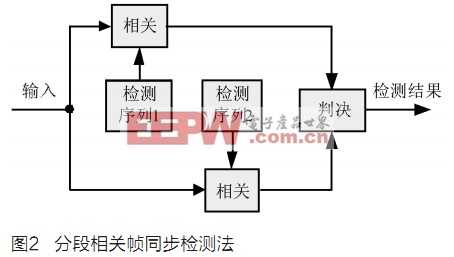

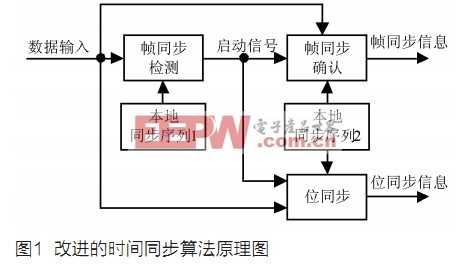

基于互相关的帧同步算法对载波频偏的容忍度与本地同步序列的长度成反比。所以,为了进一步减少帧同步的漏同步概率,在将本地同步序列分成帧同步检测和帧同步确认两部分的基础上,本文的帧同步检测采用如图2所示的分段相关法。在分段相关的帧同步检测算法中,用于帧同步检测的本地同步序列1等分为检测序列1和检测序列2两段,然后用这两段检测序列同时与输入信号进行相关,只要一个相关结果大于门限,就认为帧同步检测成功。

本文引用地址:https://www.eepw.com.cn/article/116957.htm

为了使帧同步算法更适于在FPGA中实现,本文对传统相关器进行了改进,实现方法如下:

首先对接收信号进行抽样判决(即将大于0信号的判决为“1”,否则判决为“0”),将接收信号变换为由“0”和“1”组成的序列![]() ,然后再与用于本地同步序列

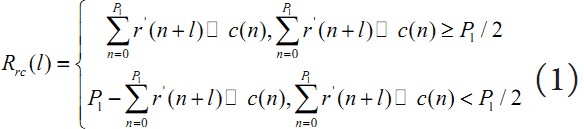

,然后再与用于本地同步序列![]() (用于帧同步检测的本地同步序列)进行相关运算。其中,相关函数可以定义为:

(用于帧同步检测的本地同步序列)进行相关运算。其中,相关函数可以定义为:

其中,![]() 表示同或,

表示同或,![]() 表示同步序列长度。考虑到接收信号

表示同步序列长度。考虑到接收信号![]() 中的数据块与本地同步序列c(n)无关,并忽略噪声的影响,可以得到:

中的数据块与本地同步序列c(n)无关,并忽略噪声的影响,可以得到:

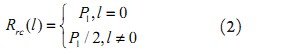

即,只有在![]() 时,出现相关峰

时,出现相关峰![]() 。

。

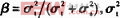

使用上述相关方法,载波频偏引起的接收信号幅度变化不会影响相关峰幅度,只有在频偏引起接收抽样序列![]() 在发生反相时,相关结果小(如当

在发生反相时,相关结果小(如当![]() 在中间位置反相时,前半段相关结果为

在中间位置反相时,前半段相关结果为![]() ,后半段相关结果为0,从而导致

,后半段相关结果为0,从而导致![]() )。而由于本文的帧同步检测使用分段相关的方法,通常情况下载波频偏引起接收同步序列在每个分段都产生反相的可能性很小,所以可以有效防止载波频偏引起漏同步发生的概率。

)。而由于本文的帧同步检测使用分段相关的方法,通常情况下载波频偏引起接收同步序列在每个分段都产生反相的可能性很小,所以可以有效防止载波频偏引起漏同步发生的概率。

评论