STM-1并行帧同步系统的设计与FPGA实现

同步技术在数字通信系统中是非常重要的技术,一般有位(码元)同步、字(码组)同步、载波同步和帧同步,对于网络系统来说还有网同步。现代SDH数字传输网是全网同步的数字传送网络,对于接收端的数据处理,首先要从同步数据流中提取帧同步信息,帧同步提取性能的优劣直接影响整个数据的处理质量与整个系统的性能。使用FPGA技术可以实现同步系统的模块化、小型化和芯片化,得到稳定可靠的帧同步器。

并行帧同步系统

SDH中的基本传输模块为STM-1,传输速率为155.52Mbps。如果采用传统的串行帧同步电路,电路需监测接收信号是否与帧同步信号一致,如果不一致则漂移1比特后再次监测是否和帧同步信号一致,如此反复。一边1比特1比特地漂移,一边搜索和帧同步信号一致的地方。所以整个逻辑电路要求工作在155.52MHz时钟频率,目前的FPGA器件工艺条件下很难得到稳定的工作性能。

针对这一问题,本文采用并行帧同步法实现STM-1码流帧同步信息的提取,系统功能框图如图1所示。在系统中,只有16比特移位寄存器工作在155.52MHz时钟频率,其余模块工作频率为STM-1码流的字节时钟19.44MHz,从而大大降低了电路时序设计难度,提高了系统的稳定性与可靠性,同时显著降低了功耗。

图1:采用并行帧同步法实现STM-1码流帧同步信息提取的系统功能框图。

根据ITU-T G.707建议的规定,SDH中采用以字节为基础的集中插入的帧同步码组,STM-1帧结构中有6个字节,即48个比特作为帧同步码组,排列为:第一行的第1列到第六列为A1A1A1A2A2A2(A1=11110110B,A2=00101000B)。为避免使帧同步电路复杂化,没有必要使用A1、A2的所有字节。根据最坏帧恢复时间参数,这里选取STM-1帧第一行的第3列与第4列16个比特,即相邻的A1A2字节作为帧同步码组。

STM-1比特码流在155.52MHz时钟控制下串行移入16比特移位寄存器。为了确定输入串行比特码流的字节边界,通过9个并行置数的字节寄存器(reg0~reg8)在19.44MHz时钟控制下对输入码流缓存,其中reg0缓存16比特移位寄存器的第0 比特到第7比特,reg1缓存16比特移位寄存器的第1比特到第8比特,依此类推。缓存后的字节数据经一个9选1的多路选择器(MUX)构成系统内部的8比特宽数据总线,再由比较器和同步校验状态机判断帧同步情况,产生帧头指示信号。同时内部数据总线的内容输出产生时钟周期为19.44MHz 的STM-1字节码流,完成对STM-1码流的串并转换。

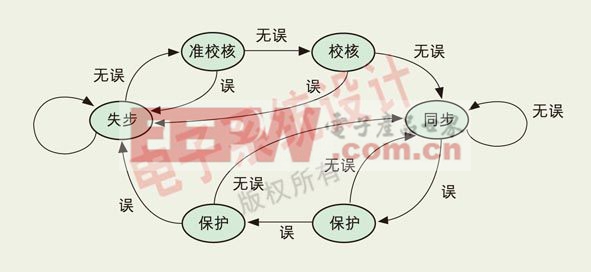

在帧同步方式中定义了失步状态、准校核状态、校核状态、同步状态和保护状态五种状态。状态转移图如图2所示。

图2:帧同步系统工作状态转移图。

在失步状态下,系统监测9个缓冲寄存器中的内容是否与A1字节(11110110B)一致。如果一致则进入准校核状态,表示已找到STM-1码流的字节边界,令多路选择器的输出(即系统内部数据总线)锁定为检测到与A1字节一致的缓冲寄存器的输出;如果不一致则维持失步状态。在准校核状态,如果内部数据总线为A2字节(00101000B)则进入校核状态,表示已发现一次帧同步码组;如果内部数据总线为A1字节则维持准校核状态;否则返回失步状态。在校核状态,漂移1个帧长(125μs)再次检测是否为A1A2字节,如果一致就转入同步状态,输出帧头指示信号;如果不一致就返回失步状态。

在同步状态下,要不断地漂移1个帧长,检查是否和帧同步码组一致。这时,由于误比特的存在,会发生接收信号和帧同步码组不一致的情况。因某1次的不一致就由同步状态转换为失步状态的话将会引起伪失步,应避免这种情况的发生。本同步系统在发生1次接收信号和帧同步码组不一致时,进入保护状态,只有连续3次不一致才转换到失步状态。在保护状态,如果漂移一个帧长后监测到帧同步码组,就返回同步状态;同时在保护状态也要产生帧头指示信号。

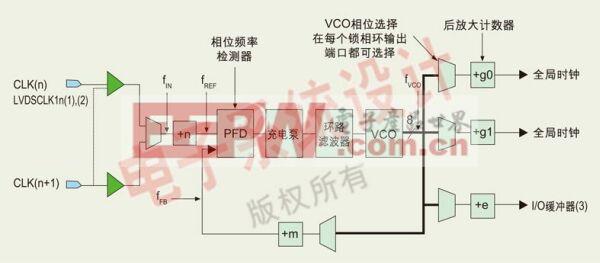

图3:Cyclone器件内置锁相环原理框图。

由于FPGA中寄存器资源丰富,所以状态机状态编码采用独热(one-hot)编码,减少状态译码电路中组合电路的复杂度,便于满足时序要求和布局布线。在状态机Verilog代码编写时,将状态转移单独写成一个always模块,将状态的操作和判断写到另一个always模块中。与将状态机的所有逻辑用一个always语句块描述相比,本设计所采用的代码风格不仅便于代码的阅读、理解、维护,更重要的是利于综合器优化代码,利于用户添加合适的时序约束条件,利于布局布线器实现设计。

在Altera的低成本的Cyclone系列器件中,有一种经过简化的快速锁相环(Fast PLL),可完成时钟的倍频、分频、相移、占空比调整和外部时钟输出,能够利用FPGA内部的全局时钟网络进行系统级时钟管理和时钟偏移(clock skew)控制,同步内部系统时钟与片外时钟,最小化时钟延迟和时钟偏移,调整tco(时钟到输出时间)和tsu(建立时间)。锁相环的原理框图如图3所示。在Altera公司的QuartusII集成开发平台中,通过调用可参数化的宏模块altpll,设置其基本参数就可以得到所需的锁相环性能,产生系统时钟信号。

本电路中需要两个时钟信号,一个是155.52MHz的STM-1比特时钟,一个是19.44MHz的STM-1字节时钟。除16比特移位寄存器工作在155.52MHz时钟频率外,整个系统都使用19.44MHz时钟。所以这里由外部晶振提供19.44MHz高稳定性的全局时钟信号,由器件内置锁相环产生8倍频时钟信号。这里设置锁相环工作在Normal模式,反馈路径补偿了输入晶振时钟与器件内到达寄存器的时钟信号之间的布线与逻辑延迟,减小时钟偏移,保证输入时钟与倍频产生的时钟之间的稳定相位关系。Normal模式下锁相环输入标准时钟与产生时钟之间的相位关系如图4所示。

图4:Normal模式锁相环时钟相位关系图。

综合与验证

首先使用Altera公司的QuartusII集成开发平台进行逻辑综合与静态时序分析(Static Timing Analysis)。选择器件型号为Cyclone系列的EP1C6T144C8。由于16比特移位寄存器工作在155.52MHz时钟频率下,为了使这部分电路能稳定可靠地工作,在综合器的设置中必须选择速度优先的优化技术,并对相关路径设计严格的时序约束条件,同时在布局布线器的设置中选择物理综合(Physical Synthesis)优化技术,否则移位寄存器将不能正确地缓存每比特码流数据。

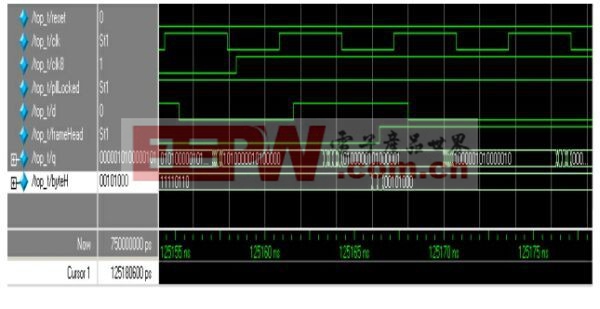

由于QuartusII工具通过NativeLink技术无缝地支持第三方仿真工具,这里采用Mentor Graphics公司的ModelSim工具提取QuartusII产生的Verilog输出网表文件和标准延时格式(Standard Delay Format)文件,进行RTL级功能仿真与门级时序仿真。由于QuartusII支持的仿真测试向量文件为图形格式的VWF(Vector Waveform File)文件,不支持Verilog文本测试向量,在测试大型设计项目时,图形格式测试向量的编写效率低、可读性差、不易于修改和维护。而ModelSim作为业界标准的硬件描述语言仿真平台,支持高效简洁的Verilog文本测试向量输入,大大提高了测试向量编写的有效性和准确性。同时ModelSim的仿真运算速度也远高于QuartusII集成的仿真工具,可大大缩短系统开发周期,加快设计进程。门级时序仿真得到的波形如图5所示。

图5:系统门级仿真波形。

图5中clk8为晶振产生的19.44MHz时钟,clk为FPGA内置锁相环8倍频产生的155.52MHz时钟,d为输入的STM-1比特码流,frameHead信号为产生的帧头指示信号,byteH为串并转换后得到的STM-1字节码流。由图可知,在连续接收到两次正确的帧同步码组后,系统进入同步状态,输出帧头指示信号。

本文小结

本文提出了高速率STM-1码流并行帧同步系统的设计方案,并在实际FPGA器件中实现了物理验证,得到了稳定可靠的工作电路。这里采用的是将1个串行码流转换为8个并行码流的并行计算技术,对于STM-4、STM-16等更高速率的码流,可以将串行码流转换为更多的并行码流,系统设计方案无需作大的调整,就可以实现高速码流的帧同步系统。

评论