用PLD简化边界扫描测试

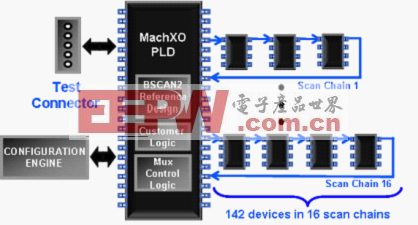

此应用使用莱迪思的多个边界扫描端口连接器(BSCAN2)参考设计。BSCAN2参考设计可免费从莱迪思的网站上下载,根据应用的需要,可以对HDL源代码进行修改。该参考设计允许连接多达8个子链路到一个边界扫描测试接口。多个BSCAN2示例可以级联在一起,以增加可用的子链路的数目。这个设计使用两个BSCAN2示例实现16个子链路。BSCAN2还可以启用不同的测试时钟用于每一个子链路。此功能是用来加速电路板调试和生产测试,导致电路板的制成时间减少了60%。

本文引用地址:https://www.eepw.com.cn/article/111150.htm

图3:在边界扫描控制应用中的MachXO - 640

总结

基于PLD的边界扫描控制解决方案将一个长的扫描链路划分成更小的子链路,改进了故障检测和隔离。通过去除电压转换器和缓冲器,在同一块集成电路中整合了定制逻辑,加强了自动化功能,可编程逻辑器件提供了一个优越的替代ASSP的方案。基于PLD的解决方案使设计人员降低了电路板的成本,简化了电路板的布局,减少了测试时间,并支持更大的系统集成。

评论