用PLD简化边界扫描测试

解决特殊要求

本文引用地址:https://www.eepw.com.cn/article/111150.htm在扫描链中的一些器件通常有特殊的要求。例如,一块电路板上可能同时拥有ASIC / ASSP器件和可编程逻辑器件。ASIC / ASSP器件只能够工作在一个模式,要么是主模式,要么是从模式。通常根据对JTAG主方的用户输入,需要边界扫描控制器从一种模式切换到其他的模式。同样,往往通过JTAG接口对可编程逻辑器件进行配置,有可能需要实现自定义逻辑,对两个不同的JTAG主方进行选择,一个用于测试,而另外一个用于对可编程逻辑器件进行配置。有一些特殊要求的实例,根据个案情况必须采取不同的管理方法,而且往往需要额外的外部硬件。

针对边界扫描控制的基于ASSP的解决方案

设计人员通常用ASSP来应对以上所述的挑战。 ASSP改进了大型电路板上的故障检测和隔离,不再把较长的扫描链路划分成更小的链路。但是,仍然存在着许多与使用ASSP相关的问题:

ASSP不能去除使用电压转换器, ASSP有固定的电平,不支持较新的低电压I / O接口。因此仍然需要电压转换器。

ASSP并不能去除需要缓冲, ASSP有固定的端口,这意味着在较大的子链路上仍然会观察到偏移效应。

自定义的单芯片解决方案并不可行 - ASSP需要额外的逻辑来解决特殊的要求。

ASSP需要大量的人工干预,这些解决方案中,设计人员必须改变电路板的跳线设置,添加或删除子链路。因此需要大量的人工干预,以便进行调试和生产测试。

针对边界扫描控制的基于PLD的解决方案

现在很多设计人员在大的电路板上使用PLD实现边界扫描控制。在一个典型的可编程逻辑器件的边界扫描控制应用中,设计人员在PLD中实现多边界扫描端口连接器。将多个端口扫描连接在一起的关键是将一个长的扫描链路划分成更小的子链链路。将长扫描链路划分成更小的子链路,通过软件控制添加或删除子链路,这样使得故障检测和隔离更加容易。有特殊要求的器件可以放置到单独的子链路,使复杂的系统变成简单的测试。为了改进测试时间,设计人员经常将慢的器件放至单独的子链路,针对较慢的和更快的子链路,使用不同的测试时钟。

现代PLD拥有多个I/ O bank,可单独配置以支持I/O工作在不同的电压。例如,莱迪思半导体公司的MachXO PLD具有能够放置LVCMOS输入到任何I / O bank的功能,因此可以方便地通过可编程逻辑器件实现电压转换。

针对LVCMOS输出,一些PLD提供能够调整驱动强度的功能。设计人员利用这个功能来增加高扇出控制信号的驱动能力。通过将长的扫描链路分成较短的子链路,以及增加高扇出信号的驱动强度,设计人员去除了缓冲控制信号。这可以简化电路板的布局,因为电路板设计人员不必构建精确的偏移匹配网络来分配高扇出信号。同样,通过减少电压转换和连接要求,设计人员可以降低对电路板面积的要求,使得布线有更大的余地。

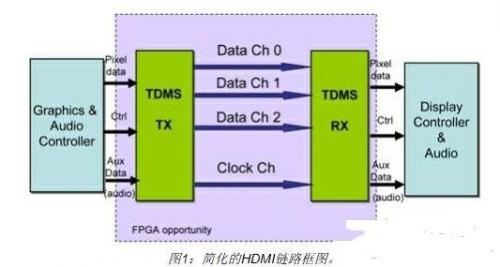

PLD用于边界扫描控制的电路板通常包括FPGA。使用JTAG接口对FPGA进行配置时,设计人员还在执行边界扫描控制的可编程逻辑器件中实现了复用器逻辑。这提供了一个更大的系统集成度。通过去除电压转换器、缓冲器和实现定制解决方案的额外逻辑,可编程逻辑器件提供比ASSP成本更低的解决方案。通过JTAG主方软件,可控制添加和删除子链路,因此减少了人工干预。

边界扫描控制器的应用

图3展示了可编程逻辑器件用于边界扫描控制应用的实例。在这个例子中,莱迪思的MachXO – 640器件用来实现多边界扫描端口连接器,在16个子链路中将142个器件连接在一起。该MachXO器件还实现了多路逻辑,可以在测试接口和配置接口之间进行选择。在同一个PLD中,其余的查找表被用来实现额外的用户逻辑。

评论