近访硅谷:Mentor加速IC测试工具

12月4日(周五),我们见到了Mentro Graphic公司IC诊断工具部门负责人。在硅谷,EDA工具很是热门的。每次Globalpress公司组织的活动中,EDA厂商都是不可或缺的部分。

我也和韩国、我国台湾的编辑聊了一下,在他们的国家和地区,读者和咱们一样,也比较喜欢用芯片做应用,例如单片机。可惜在硅谷采访,单片机公司凤毛麟角,美国人认为单片机是较低技术,65nm、45nm制程、高密度芯片才是高端技术。

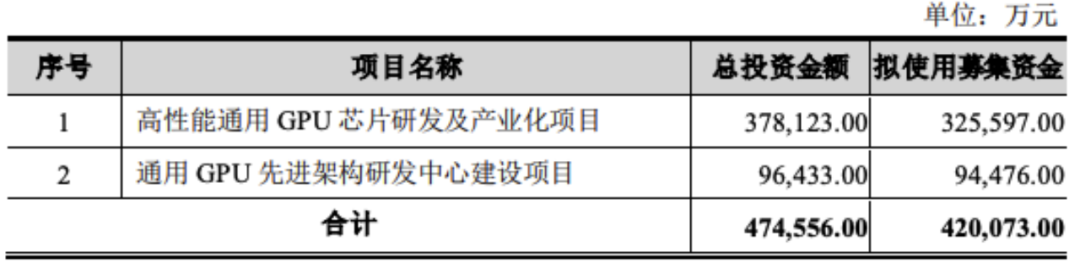

照片 Mentor Graphics公司设计到芯片(Design to Silicon)部门副总裁兼总经理Joseph Sawicki:随着IC制程节点从90nm向65nm和45nm延伸,需要测试的数据量会激增,相应地会带来测试成本的提高。例如,从90nm到65nm时,由于增加了门数,传统测试量大量增加;同时,在速(at-speed)测试也增加了,这是由于时序和信号完整性的敏感需求;到了45nm时代,在前两者的基础上,又新增了在新节点上探测新缺陷的测试。

为了使客户应对更小的制程节点、更复杂、低功耗、混合信号SoC测试,Mentor用其获奖的嵌入式压缩和自动测试向量生成(ATPG)技术,与Mentor 2009年8月刚刚收购的LogicVision公司的内置自测试(BIST)技术结合,称为Tessent。Tessent线是业界最复杂的可测试设计(DFT)和芯片测试方案组合之一,它还包括LogicVision公司的SiliconInsight产品、Mentro的布线应用诊断工具和新发布的Tessent YieldInsight产品,可提供用于后硅(Post-silicon)的测试描述和产出分析。

照片 为了庆贺本周AsiaPress tour的采访成功,中午,大家聚集在墨西哥风味的Albequer 餐馆。本照片由台湾媒体编辑王岫晨提供(右2),他的左右都是韩国编辑(看不出来吧?他们都是两个孩子的父亲),右4、5是Globalpress公关公司的两位员工Tanya和Cecily,笔者在右6。

“近访硅谷”系列文章一览:

http://wangying1.spaces.eepw.com.cn/articles/article/item/68591

http://wangying1.spaces.eepw.com.cn/articles/article/item/68771

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。