IBM,分享混合键合新技术

来源:IBMresearch

几十年来,计算机已经从占据整个房间的机器缩小到可以戴在手腕上的设备。研究人员专注于增加单个计算机芯片上晶体管数量的密度,并且通常依赖 SOC(或片上系统)来降低成本并使设备更紧凑。但是我们开始接近我们可以将芯片的某些部分做得多小的物理极限,而其他部分在某些用例中也同样有效,即使它们不是最小的、最前沿的设计。

这就是芯片封装的重要性所在。封装是在芯片或电路板上连接集成电路的过程,随着电子设备的缩小和芯片组件本身变得越来越小,封装变得越来越复杂。IBM 于 2021 年宣布了一款组件尺寸仅为 2 纳米的芯片。随着半导体行业转向新的芯片构造方法,封装技术的进步将变得越来越重要。这种转变的一个关键部分是小芯片技术的兴起。

对小芯片的研究表明了计算的未来可能是什么样子。有许多新兴用例(如训练和运行复杂的 AI基础模型)可以从新芯片设计中受益,而不是专注于构建单片 SOC。chiplet 背后的概念有效地将 SOC 分解成多个复合部分(如 GPU、CPU、I/O 和内存),并构建对特定任务更有效的 chiplet 系统。就人工智能而言,你可以构建一个小芯片系统,将处理单元、人工智能加速器和内存堆栈结合在一起,所有这些都在通信和共享数据,就好像它们都在同一个芯片上一样。

将小芯片从研究转向生产需要克服的最大障碍之一是小芯片在封装过程中粘合在一起的方式。迄今为止,大多数设计都使用位于金属焊盘顶部的焊料或焊料和铜的组合将小芯片连接在一起。这些方法导致键合在 150 到 30 微米之间,需要非常紧密的焊接才能有效。但是 IBM 和 ASMPT(半导体生产硬件和软件的主要供应商)的一组研究人员一直在研究一种新的方法来结合小芯片,从而大大减少空间量。

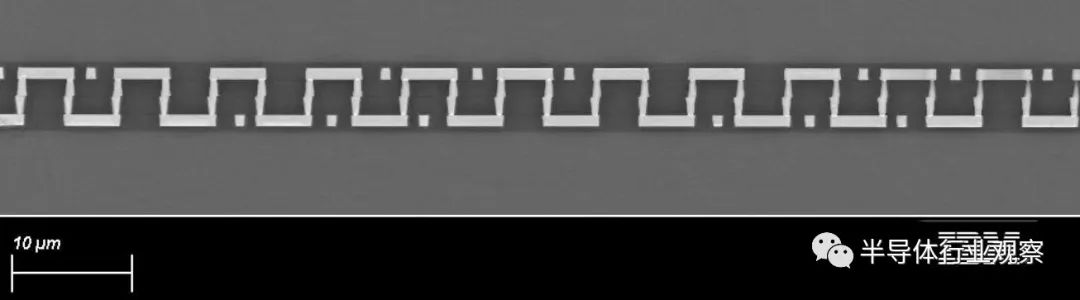

在本周于 2023 年 IEEE 电子元器件与技术会议 (ECTC) 上发表的一篇论文中,1个研究人员概述了他们的混合键合概念。他们的方法在不使用焊料的情况下,将铜和氧化物熔合在只有几个原子厚的层中。结果是小芯片之间的键合仅为 0.8 微米左右,比目前正在测试的其他方法要薄得多。

新的混合键合方法有可能增加小芯片之间的数据吞吐量,以及可以安装在给定空间中的小芯片数量,从而使小芯片系统更像单个 SOC。例如,它对于将 chiplet 技术集成到更小的设备以及提高 chiplet 的性能或其能效具有重大意义。

在团队的方法中,最艰巨的挑战是确保粘合牢固,以极小的规模去除潜在的水分或气泡。粘合层之间只有三个水分子就足以破坏层与层之间的连接。消除这种危险以及气泡,同时保持粘合在一起的各层表面清洁——并确保这一过程能够可靠地一次又一次地进行——是该团队在研究中寻求克服的主要挑战。

该团队的方法类似于芯片晶圆的键合方式,这是目前的标准行业惯例——只是规模相当小——他们一直在使用专为芯片到晶圆键合而设计的 ASMPT 机器来执行他们的测试。虽然该团队认为他们的方法可以大规模构建小芯片并将其结合在一起,但在研究 ASMPT 系统的工具方面还需要做更多的工作。

未来的系统将需要新的方法来解决计算问题,因为它们变得更加复杂和多样化,而小芯片提供了解决这些问题的潜在途径。通过混合键合,创建的系统就好像它们是单个芯片的一部分一样,未来变得更加清晰。

-End-

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。