- Cadence设计系统有限公司近日宣布高科技厂商三星电子有限公司使用Cadence统一数字流程,从RTL到GDSII,成功实现了20纳米测试芯片的流片。Cadence Encounter工具集成平台的流程与方法学的应用,满足了三星片上系统(SoC)产品对于高级20纳米工艺技术的需要。该流程处理了IP集成与验证,以及20纳米工艺的复杂设计规则。

此次成功表明了三星在高级工艺节点上设计与生产的领先地位,以及Cadence统一数字流程拓展到下一个工艺节点的实力。此外,达到这样的里程碑表明设计链的主要方

- 关键字:

三星 20nm

- 三星电子日前宣布,已经成功实现了20nm工艺试验芯片的流片,这也是迄今为止业内最先进的半导体制造工艺。三星电子此番利用了美国加州电子设计自动化企业Cadence Design Systems提供的一体化数字流程RTL-to-GDSII。

- 关键字:

三星 20nm Cortex-M0

- 近日比利时注明的独立微电子研究机构IMEC近日宣布与NVIDIA达成合作协议,共同致力于先进CMOS工艺的研发。

签署这份为期三年的协议后,NVIDIA将成为IMEC的InSite核心级别无工厂合作伙伴,能在第一时间为自己的下一代产品评估和选择先进的制造工艺和设计技术,还将携手研发3D三栅极晶体管、后20nm工艺光刻应用等技术。

- 关键字:

NVIDIA 20nm

- 集邦科技发布近日报告称,明年全球闪存芯片销售额将达到215亿美元,同比上涨16%,但是其平均价格将同比下降35%。

集邦科技称,新款智能机、平板机的发布以及春节期间的采购将缓解明年一季度闪存市场受到的季节性销售因素影响。到二季度时,闪存市场的供需就会更加平衡,价格下降幅度不会太大。

- 关键字:

NAND 20nm

- 法国两家半导体研究机构CEA-Leti和Circuits Multi Projets日前宣布,他们将在一项定于明年9月份启动的300mm多项目晶片研究计划中采用基于20nm制程的全耗尽型SOI工艺制作这种芯片。这次 多项目晶片研究计划是由欧洲一个专门研究SOI技术的学术团体EuroSOI+负责参与支持的。

所谓的多项目芯片(multi-project wafer:MPW),指的是在同一片晶圆上采用相同的制程制出不同电路设计的IC芯片,这样可以为多家厂商或研究机构的IC设计验证节约成本,非常适用于

- 关键字:

FDSOI 20nm

- 据electronicsweekly网站报道,台积电公司近日宣称已经开发出一套采用Finfet双门立体晶体管技术制作的高性能22/20nm CMOS制程,并已经采用这种制程造出了面积仅0.1平方微米的SRAM单元(内含6个CMOS微晶体管),据称这种制程生产的芯片产品在0.45V工作 电压条件下的信号噪声仅为0.09V。

这种Finfet制程技术采用了双外延(dual-epitaxy)和多重硅应变(multiple stressors,指应用多种应力源增强沟道载流子迁移率的技术)技术,台积电宣称

- 关键字:

台积电 立体晶体管 20nm

- Applied Materials公司近日宣布开发出了一种新的化学气相淀积(CVD)技术,这种技术能为20nm及更高等级制程的存储/逻辑电路用晶体管淀积高质量的 隔离层结构。据Applied Materials公司宣称,这些隔离结构的深宽比可超过30:1,比目前工艺对隔离结构的要求高出5倍左右。

这项技术使用了Applied Materials公司名为Eterna流动式化学气相沉积系统(Flowable CVD:FCVD)的技术专利,淀积层材料可以在液体形态下自由流动到需要填充的各种形状的结构中

- 关键字:

应用材料 CVD 20nm

- 南韩内存厂商Hynix公司日前宣布已开始量产20nm制程级别64Gb NAND闪存芯片,这款芯片是在公司位于Cheong-ju的300mm M11工厂生产的。Hynix公司表示,升级为2xnm制程节点后,芯片的生产率相比3xnm制程提升了60%,芯片的成本也有所降低,智能手机,SSD 硬盘等的NAND闪存容量则将大有增长。

Hynix Cheong-ju M11工厂

Hynix公司称首款基于2xnm制程的NAND闪存芯片产品将于今年年底上市销售。Hynix公司虽然不是I

- 关键字:

Hynix NAND 20nm

- ARM与其长期代工合作伙伴台积电公司近日宣布双方已经正式签署了由台积电公司使用28/20nm制程技术为ARM公司代工新款SOC芯片的合作协议。根据这份协议,台积电公司将为ARM代工多款专门针对台积电的制程技术优化过的ARM处理器产品,另外,双方还将合作开发专门针对台积电的制程技术优化过的 处理器核心设计技术,这些技术将被应用到包括无线功能,便携式计算,平板电脑产品,高性能计算等应用范围的产品中去。

去年,ARM曾经与台积电的死对头GlobalFoundries签订了一项合作协议,不过那份协议

- 关键字:

ARM 20nm SOC

- 据台积电公司负责技术研发的副总裁蒋尚义表示,2011年台积电从荷兰ASML公司订购的极紫外(EUV,波长13.5nm)光刻设备将运抵厂内,这批订 购的设备将为台积电公司2013年将公司制程能力升级到20nm级别铺平道路.蒋尚义是在本月24日举办的台积电技术论坛会议上说出这番话的,他同时还指 出EUV光刻技术要想投入商用还需要更加成熟,另外他还透露这批订购的EUV光刻工具每小时能刻制100片晶圆。

台积电首批EUV光刻设备将被安装在300mm Fab12工厂内,而台积电未来的研发重点则将放在2

- 关键字:

台积电 20nm 光刻设备

- 台积电总裁张忠谋认为,虽然近期IC业的形势越来越好, 但是产业还是面临诸多挑战。

在近期举行的台积电技术会上张忠谋表示,摩尔定律正在减缓和芯片制造成本越来越高,因此台积电将比过去在芯片制造商与代工之间更加加强紧密合作。

它对于大家说,此种合作关系要从芯片设计开始, 并相信未来台积电会做得更好。

它同时指出,加强合作要依技术为先。从技术层面, 那些老的,包括新的代工竞争者, 如GlobalFoundries,Samsung及UMC,对于台积电都能构成大的威胁。

非常幸运, 大部分

- 关键字:

台积电 20nm CMOS

- 继Intel、美光上个月宣布投产25nm NAND闪存芯片后,韩国两大存储厂三星和海力士近日也宣布了自家的30nm以下工艺NAND闪存投产计划。

海力士将采用26nm工艺生产容量为64Gb的NAND闪存芯片,这和Intel、美光首批投产的25nm芯片容量一致。而三星则计划在今年第二季度投产27nm NAND闪存。

海力士表示,和30nm工艺相比,新工艺的闪存芯片的产能将翻一番,成本也将大幅度降低。根据韩国当地媒体的报道,海力士将在今年第三季度开始量产 26nm闪存芯片。在这一点上三星已经占

- 关键字:

三星 20nm NAND闪存 海力士

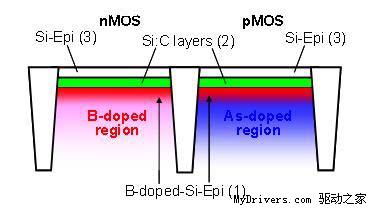

- 东芝公司今天在美国马里兰州巴尔的摩市举行的IEDM半导体技术会议上宣布,其20nm级CMOS工艺技术获得了重大突破,开启了使用体硅CMOS工艺制造下一代超大规模集成电路设备的大门,成为业界首个能够投入实际生产的20nm级CMOS工艺。东芝表示,他们通过对晶体管沟道的掺杂材料进行改善,实现了这次突破。

在传统工艺中,由于电子活动性降低,通常认为体硅(Bulk)CMOS在20nm级制程下已经很难实现。但东芝在沟道构造中使用了三层材料,解决了这一问题,成功实现了20nm级的体硅CMOS。这三层材料

- 关键字:

东芝 CMOS 20nm

- 据业者透露,东芝及其闪存合作伙伴SanDisk计划要在明年下半年开始采用20nm级别制程来量产NAND闪存芯片。另外两家公司在日本本州四日市(Yokkaichi)合资兴建的闪存芯片厂将逐月增大闪存芯片的产能,直至达到20万片的产能水平。

东芝公司最近已经开始32nm制程3bpc(每存储单元3bit数据)闪存芯片的量产,按原先的计划,合资的四日市芯片厂32nm制程芯片的产量应在今年底前达到总产量的50%左右,不过按目前的产能规划来看,实际的量产实施时间看来已经会有所拖延。

另一方面,对手In

- 关键字:

SanDisk 20nm NAND 闪存芯片

- 在今后的2年~3年内,NAND闪存的集成度仍将保持目前的发展速度。具体来说,到2011年~2012年,通过采用2Xnm的制造工艺与3位/单元~4位/单元的多值技术,NAND闪存很有可能实现128Gb的容量。

但是,如果要实现超过128Gb的更大容量,恐怕就需要全新的技术。目前正在量产的NAND闪存通常都使用浮栅结构的存储单元。许多工程师也认为,2011年~2012年将量产的2Xnm工艺及其后的20nm工艺仍可采用现有的浮栅结构的存储单元。但据SanDisk公司分析,当工艺发展到20nm以下时,从

- 关键字:

SanDisk 20nm NAND

20nm介绍

您好,目前还没有人创建词条20nm!

欢迎您创建该词条,阐述对20nm的理解,并与今后在此搜索20nm的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473