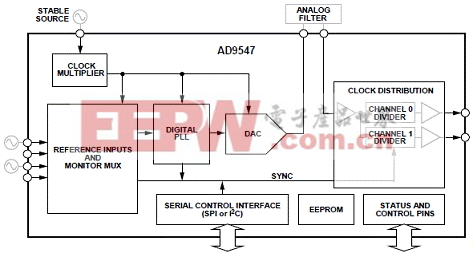

- AD9547是双路/四路输入网络时钟发生器/同步器,能为许多系统包括同步光网络(SONET/SDH)提供同步.输入基准频率从1 kHz 到750 MHz,频率监视1ppm,输出频率高达450MHz,主要应用在网络同步,OC-192的SONET/SDH时钟,无线基站

- 关键字:

同步 方案 发生 时钟 AD9547 网络 ADI

- 应用于绿色电子产品的首要高性能、高能效硅方案供应商安森美半导体(宣布扩充公司的时钟驱动器系列,推出NB7L585、NB7L585R、NB7V585M和NB7V586M差分2:1多工器输入至1:6器件,以及带均衡功能的NB6HQ14M和NB7HQ14M 1:4扇出时钟/数据驱动器。

NB6HQ14M和NB7HQ14M高性能差分1:4电流模式逻辑(CML)时钟驱动器中集成了可选择的均衡器接收器。当与工作数据率高达6.5 Gbps或10 Gbps的数据通道串联布置时,输入将补偿退化的信号,输出4个

- 关键字:

安森美 时钟 数据驱动IC

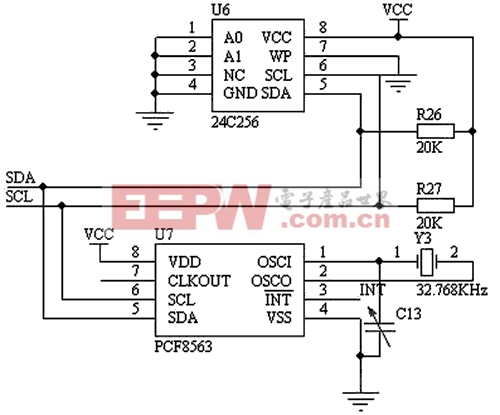

- 日历时钟和存储电路

如下图所示,由EEPROM24C256和日历时钟芯片PCF8563组成。24C256是一款低电压、串行接口,容量为256K的存储器,用于存储测量的血压值。PCF8563是PHILIPS公司推出的一款工业级内含I2C总线的具

- 关键字:

电路 键盘 显示 存储 时钟 日历

- 随着电子技术的不断发展,数据的传输速度越来越快,高速时钟的应用日益广泛,如何保证时钟在高速跳变过程中的信号完整性、抖动、功耗等问题,已逐渐成为关注的问题。传统的时钟设计方法大多依靠经验和理论计算,但是随着时钟频率越来越高,时钟的电磁环境日趋复杂,时钟的传输线效应、过冲/欠冲、反射、振铃效应、趋肤效应都成为影响时钟设计的关键因素,只有使用现代科技手段,利用计算机的强大计算能力进行仿真才能够保证时钟电路设计成功。 HyperLynx是Mentor(Graphics开发的一款板级信号完整性的仿真工具。它可以进行

- 关键字:

HyperLynx PECL 交流耦合 时钟

- CAN是事件触发的通信协议,它

- 关键字:

CAN 时钟

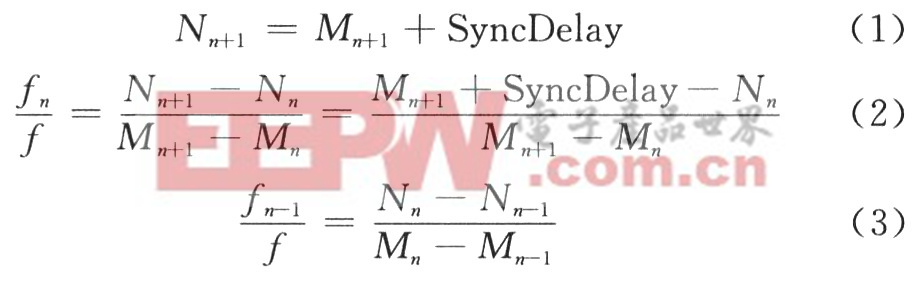

- FPGA的时钟频率同步设计,引 言

网络化运动控制是未来运动控制的发展趋势,随着高速加工技术的发展,对网络节点间的时间同步精度提出了更高的要求。如造纸机械,运行速度为1 500~1 800m/min,同步运行的电机之间1μs的时间同步误差将

- 关键字:

设计 同步 频率 时钟 FPGA

- 引 言

由于指令的速度不断加快,单片机在各个方面的性能大为提高,比如多个单片机之间的时钟同步。Silicon Labs公司的C8051F系列单片机的执行速度最高可以达到100MIPS,这使得更高精度的时钟同步成为可能。时

- 关键字:

同步 技术 时钟 RS422 F1 C8051

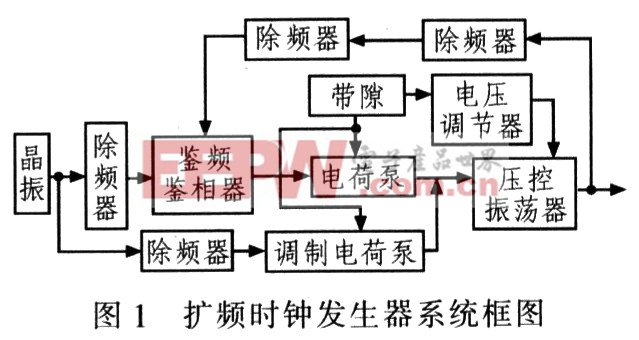

- 自动反馈调节时钟恢复电路设计,0 引言

信息技术的迅猛发展使得人们对数据传输交换的速度要求越来越高,因此,各种高速接口总线规范应运而生,从USBl.1到USB3.0,从PATA到SATA,从PCI总线到PCI―Express,其接口总线速度也由最初的Kbyte发展

- 关键字:

恢复 电路设计 时钟 调节 反馈 自动 PLL 时钟恢复 自动反馈 CDR 高速串行总线

- 日前,德州仪器 (TI) 宣布推出业界最小型 4 通道、低功耗、低抖动正弦至正弦波时钟缓冲器。作为正弦波时钟缓冲器系列产品中的首款产品,CDC3S04 可取代多达 3 颗具有相同频率的独立温度补偿晶体振荡器 (TCXO),从而可将板级空间与材料单 (BOM) 成本锐降近 50%。设计人员可将 CDC3S04 用于各种移动应用中,其中包括手机 (UMTS/WCDMA/GSM)、智能电话、移动因特网设备 (MID)、超移动 PC (UMPC)、导航设备以及全球定位系统 (GPS)。

CDC3S0

- 关键字:

TI 时钟 缓冲器 CDC3S04

- 引 言

长期以来,学校、工厂等单位常用的打铃仪多采用单片机计时,计时误差每天达0.5 s,日积月累走时误差会达数分钟,甚至十多分钟,给管理造成不便。近几年来,高校、企业规模不断扩大,多校

- 关键字:

GPS 时钟 打铃

- 1 引言

DP(DisplayPort)接口标准旨在寻求代替计算机的数字视频接口DVI(Digital Visual Interface)、LCD显示器的低压差分信号LVDS(Low Voltage Differential Signal),作为设备间和设备内的工业标准,并在若干领

- 关键字:

系统 参数 研究 发生器 时钟 DP 标准 扩频 基于 LCD

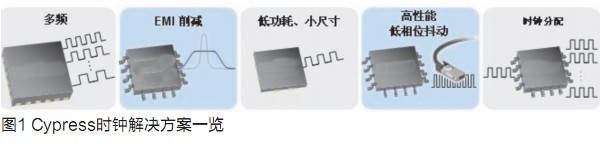

- 时钟按功能分,可分为多频、EMI削减、低功耗小尺寸、高性能低相位抖动、时钟分配等(如图1)。

多频:就是在同一个晶振里可产生不同频率的时钟源。例如,晶振本身也许是一个37kHz的,你可以从这个频率上面去延伸开来,像ATM需要25MHz,SDH需要19.44MHz……这一个器件可产生系统里需要的所有频率,并且这些频率之间可以相互没有任何关系。

EMI削减:该器件已拥有多频器件的所有功能,除此之外,EMI(电磁干扰)削减特点突出。

低功耗、小尺寸:主要针对

- 关键字:

Cypress 时钟 EMI 低功耗

- 当前,时钟产品的推出速度越来越快,时钟需要满足的标准也在不断发展,时钟需要更高的性能、更高的精度,系统尺寸也需要越来越小,在存储、通信与网络、上网本、开关稳压器的相位同步、FPGA等方面的应用成为热门。

- 关键字:

Cypress 时钟 计时 抖动 EMI削减 可编程 200909

时钟介绍

时钟的概念多用于数字语音交换机,因为数字交换对于以时隙为单位的交换单位而言,其时间性的重要程度非常高。为保证交换机的正常工作,每套交换系统都必须配置精度极高的时钟发生器,用于交换系统内部工作。系统内部的时钟一般称为内时钟。

如果两套交换系统协调工作,那么必须要在两套系统之家,也就是两个内时钟之间进行协调,保证两个时钟同步工作,这就是时钟同步,对于每套系统的内时钟而言,另一套系统的内时钟即为外时钟 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473