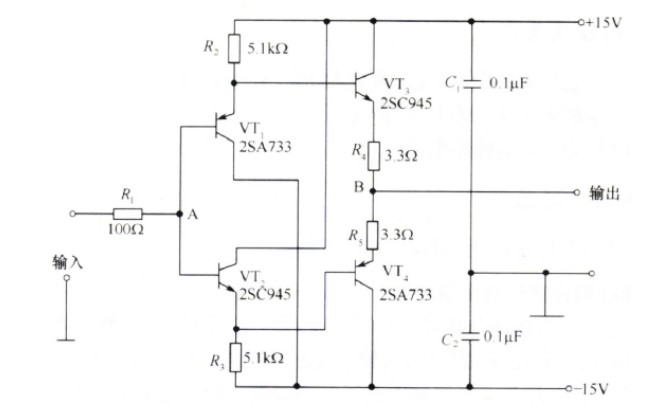

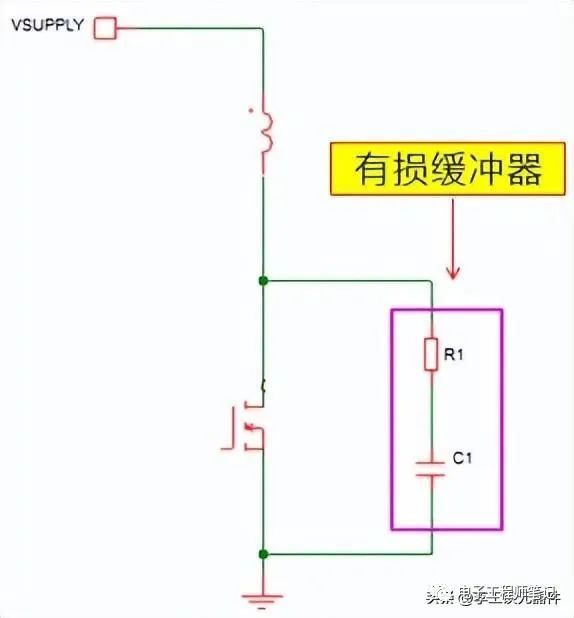

今天给大家分享的是:缓冲电路、缓冲电路设计、缓冲电路功耗计算。一、什么是缓冲器?缓冲器是一种对电压尖峰、振铃和振荡效应的电路保护形式。缓冲器通过钳位电压尖峰但不改变振铃频率。缓冲电路设计通常都比较复杂,设计一个好的缓冲电路需要对电路有很深入的了解,这篇文章就来详细介绍一下缓冲电路、缓冲电路设计、缓冲电路功耗计算。二、缓冲器电路设计的一般分类1、有损或者散耗缓冲电路有损缓冲电路是一种消耗功率的电路,对于电源效率要求比较高的话,这就一个很大的缺点,但是容易设计。耗散缓冲器使用电阻,有时候也使用二极管作为耗散元

关键字:

缓冲器 缓冲电路 电路设计

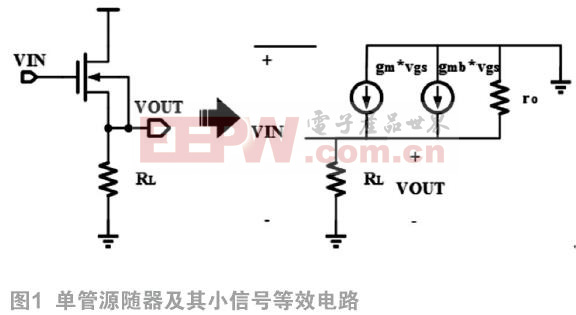

提出一种基于TSMC40LP工艺的输入信号缓冲器,用于12 bit 4 GSPS ADC的缓冲器设计。本缓冲器采用开环源随器结构,由于工艺角和温度变化,开环结构的缓冲器的输出共模将会漂移,导致比较器的输入共模发生漂移,使得比较器的比较结果发生错误。采用Replica共模反馈的方式为主缓冲器提供共模,实现缓冲器的输出共模的稳定,避免比较器因为共模变化而工作不正常。为了达到线性度的要求,通过叠层源随器和电容,将输入信号耦合到源随器的漏端,避免了短沟道器件的沟调效应。源随器采用深N阱器件,消除了衬底偏置效应。本

关键字:

缓冲器 沟道调制效应 衬底偏置效应 线性度 201806

加外部缓冲器的远程测温电路加外部缓冲器的远程测温电路由TMP04和ADM485

关键字:

缓冲器 远程测温

概述:本文介绍了一种使用可变电压控制的电流源(VVCCS)实现的基于比较器的新型缓冲器。可跟踪电流源的应用提供了高精度的性能,不仅能减少输出节点的过冲误差,还能减少过冲误差相对输出电压的变化。同时利用0.18m

关键字:

比较器 缓冲器 电流源 VVCCS

内部集成电路总线(I2C)是一种同步串行数据通信总线,其中由主器件发起通信,从器件通过寻址机制加以控制。I2C总线上的节点很容易连接,因为只需连接两条开漏形式的信号线(SDA用于数据,SCL用于时钟)。这些线上的电容

关键字:

I2C总线 缓冲器 PCA9605

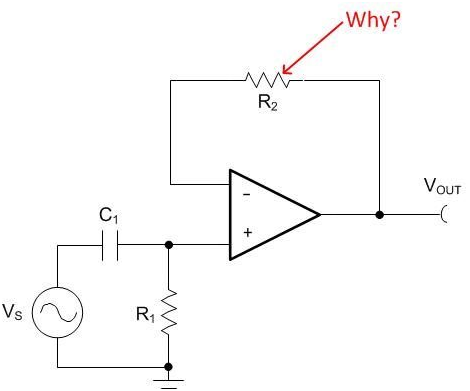

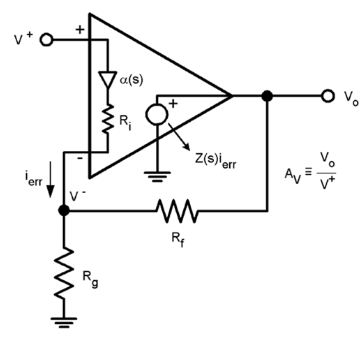

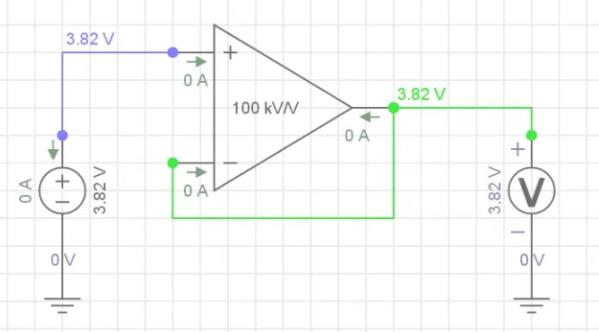

每当检查年轻工程师的电路原理图或印刷电路板 (PCB) 布局布线时,我都要挑选几个项目,问他们“为什么这么做?”为什么你选择这个组件?为什么把它布置在 PCB 的这个位置?之所以问这些问题是因为工程师在做出每个设计决策时都应该有合理的理由。 例如,在配置成缓冲器的运算放大器反馈路径中有一个电阻器,应该马上想到“这是为什么呢?”

图 1:在反馈路径中包含电阻器的运算放大器缓冲器电路 令人难以接受的实际情况

关键字:

缓冲器 电阻器

导读:本文主要讲述的是缓冲器的原理,感兴趣的盆友们快来学习一下吧~~~很涨姿势的哦~~~

1.缓冲器原理--简介

缓冲器是缓冲寄存器的简称,它分为输入缓冲器和输出缓冲器两种。前者的作用是将外设送来的数据暂时存放,以便处理器将它取走;而后者的作用是用来暂时存放处理器送往外设的数据。有了数控缓冲器,就可以使高速工作的CPU与慢速工作的外设起协调和缓冲作用,实现数据传送的同步。由于缓冲器接在数据总线上,故必须具有三态输出功能。

2.缓冲器原理--分类

缓冲器分为两种,常用缓冲器(常说缓冲

关键字:

缓冲器 缓冲器原理

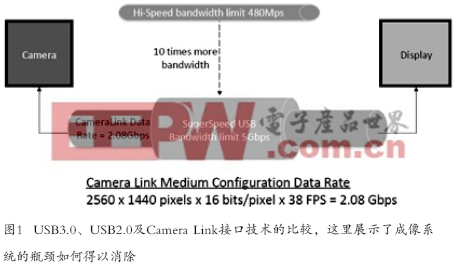

高清图像质量已经快速成为现代家庭中多媒体产品的标准配置。在该领域之外的许多应用中,更高的分辨率、更好的对比度、更大的色深和更快的帧率也都越来越受欢迎,这些应用包括安保、医疗成像和工厂生产线检测系统等等。当然,尽管增强型成像技术在不久的将来更加流行似乎是板上钉钉的事情,但这将取决于支持更高数据传输能力的先进半导体技术的发展。本文将以实例阐述半导体技术所取得的进展。

虽然USB连接标准开始并没有引起太多关注,但从上世纪90年代中期第一次脱颖而出已经改变了很多,它现在已经远远不只是为低数据速率的鼠标和

关键字:

USB FIFO 缓冲器 FPGA 显示器

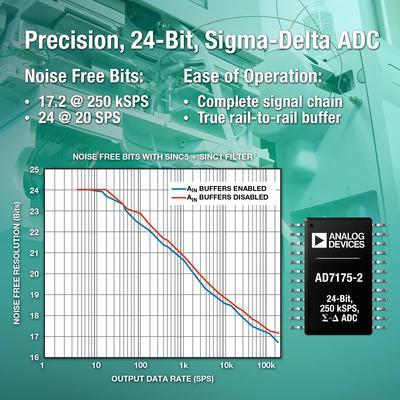

Analog Devices, Inc. 最近推出业界首款完全集成真轨到轨输入缓冲器的Σ-Δ型转换器,吞吐速率达250 kSPS,可为设计人员提供业界领先的噪声性能。

ADI发布业界首款集成真轨到轨输入缓冲器的Σ-Δ型ADC

AD7175-2 Σ-Δ型ADC在20 SPS 时具有24个无噪声位,250 kSPS 时具有17.2个无噪声位,为设计人员提供了更宽的动态范围,可实现实验室分析仪器系统所需的

关键字:

ADI 缓冲器 ADC

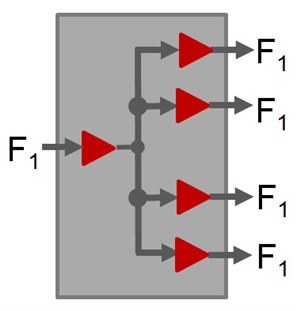

为互联网基础设施提供高性能时钟解决方案的领导厂商SiliconLabs(芯科实验室有限公司)今天宣布推出PCIExpress(PCIe)Gen1/2/3扇出缓冲器,此产品为包括服务器、存储器和交换机在内的数据中心应用而设计。针对当今领先的x86主板和服务器系统,新型的Si5310x/11x/019 PCIe缓冲器是业内最高能效的扇出缓冲器,有效扩展了Silicon Labs不断壮大的PCIe计时产品线。凭借灵活的输出数量选项,新型的PCIe缓冲器能够完整满足98%的基于x86的服务器/存储器主板设计需

关键字:

Silicon Labs 缓冲器 PCI Express

如果您在通信行业工作,那么您可能很熟悉抖动对系统性能的影响。抖动不仅会降低数据转换器的性能,而且还可在高速数字系统中产生误码。凭直觉判断,给时钟增加噪声会增大系统其它部分的噪声。因此我总是试图通过选择可带来最小附加抖动的组件来最大限度地降低总体抖动。顾名思义,附加抖动就是由位于时钟源(例如合成器或振荡器)与被计时器件之间的组件所增加的噪声。该附加噪声可增大时钟的不确定性,导致抖动增加。

在实际系统中,一个时钟源要驱动多个器件,因此可使用时钟缓冲器(通常称为扇出缓冲器)来复制信号源,提供更高的激励

关键字:

缓冲器 合成器

电流反馈 (CFB) 放大器大部分归属高速放大器范畴。近年来所推出的大量良好应用指南主要用来介绍应用电流反馈放大器的工作以及其中所遇到的主要问题。这里我们将通过简短的文字加以总结。

CFB 放大器具有一个高阻抗输入(非反相输入)、一个低阻抗输入(反相输入)以及一个输出低阻抗,如下图所示。注意:为了便于讨论,我会忽略电源引脚及禁用功能。

图 1:CFB 内部组件

只要不加载输入,非反相输入端电压便可看到高输入阻抗。非反相输入端电压在通过缓冲器时会出现在反相输

关键字:

放大器 CFB 缓冲器

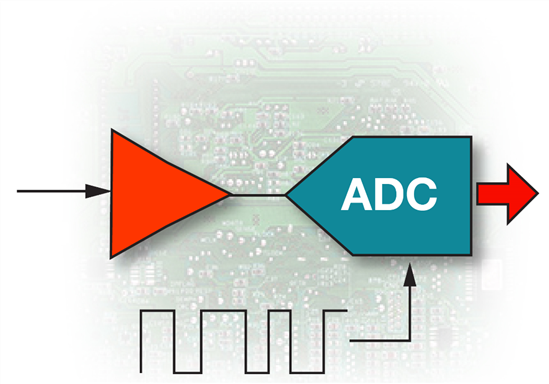

很多人都知道,抖动(这是时钟边沿不确定性)是不好的现象,其不仅可导致噪声增加,而且还会降低数据转换器的有效位数 (ENOB)。

例如,如果系统需要 100MHz 14(最小值)位的 ENOB,我们就需要抖动小于 80 飞秒的时钟!这可通过假设一个无失真的理想系统进行计算,让 SINAD 和 SNR 数值相等(见公式 2)。

接下来,使 ENOB 等于 14,我们可在大约 86db 下计算出最小 SNR。将结果带入公式 1,计算出大约为 80fs 的 tJ 值。

关键字:

时钟采样 ENOB 缓冲器

拥有模拟和数字领域的优势技术、提供领先的混合信号半导体解决方案的供应商 IDT® 公司 (Integrated Device Technology, Inc.; NASDAQ: IDTI) 日前宣布,推出一个 1.8V LVDS 时钟扇出缓冲器系列,可提供相当于 3.3V 器件的高性能 AC 特性。新的低压扇出缓冲器可使客户节省高达 60% 的功耗和散热,且不牺牲精确度、误码率和功能性。

关键字:

IDT 缓冲器 8P34S

缓冲器介绍

最基本线路构成的门电路存在着抗干扰性能差和不对称等缺点。为了克服这些缺点,可以在输出或输入端附加反相器作为缓冲级;也可以输出或输入端同时都加反相器作为缓冲级。这样组成的门电路称为带缓冲器的门电路。带缓冲输出的门电路输出端都是1个反相器,输出驱动能力仅由该输出级的管子特性决定,与各输入端所处逻辑状态无关。而不带缓冲器的门电路其输出驱动能力与输入状态有关。另一方面。带缓冲器的门电路的转移特性至少是由3 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473